# 半導体デバイス・プロセス工学

ートランジスタの動作原理と LSI のできるまでー

工学博士

横 山 新 著

2017年版

印刷、改変はできません

これはWeb掲載用の見本版です。

著作権上問題のある部分には「見本」のシールを貼ってあります。 原著が必要な方は、下記にご連絡ください。 yokoyama-shin@hiroshima-u.ac.jp

# デバイス・プロセス工学

―トランジスタの動作原理と LSI のできるまで―

## 緒言

子供の頃夢見ていた鉄腕アトムのようなロボットが、自分の生きているうちに実現出来るとは、これまで思っていなかった。しかし、最近のロボット技術の進歩は目覚しく、人間に近い、あるいは人間を超える能力を持ったロボットが実現されるのも遠い未来ではなくなった。すでに、走ったり、ボールを認識して追いかけたり、卵をつぶさずに握ったり、サッカーをしたりするロボットも登場している。このような目覚しい進歩は、機械技術だけでなく、頭脳に当たるLSI(大規模集積回路)の指数関数的な進歩によるところが大きい。LSIの進歩は、世の中を変えていく原動力として、今後も益々重要性が増すと思われる。

LSIに関する教科書は多数出版されているが、半導体物理とLSIの製作プロセスに関して、工学系の大学の学部生および大学院生にとって、納得して理解でき、かつ研究にも役立てることのできる適切なレベルの教科書は少ない。そこで、本書では、図を多用し、出来るだけ数式を減らして直感的に理解できることを心がけた。LSIにおける基本デバイスは、pn接合、MOS構造、MOSトランジスタであるので、これらを中心に取り扱う。

本書が、大学の学部生、大学院生および研究者の役に立てれば幸いである。また、数式を減らし直感的理解に重きを置いたがために、誤った説明になっている箇所もあるかと思われる。ご指摘いただければ幸甚である。 2006 年 10 月

#### 改訂に当たって

- ・以下の項目について説明を加えた。「プレーナ技術」、「自己整合技術」、「基板バイアス効果」、「LSI 配線におけるリピータ」、「酸化膜中等価電荷密度」、「Si酸化膜中の不純物拡散係数」、「アレニウ スプロット」、「ワイブルプロット」。 2010 年 10 月

- ・さらに表 II.1 を改訂、「犠牲酸化」、「三次元 LSI」、「Si 貫通電極」に関する説明を加えた。チャネルストップドーピングによるしきい値電圧の例題を追加した。 2011 年 10 月

- ・表 II.1を再改訂、III.1節に例題と省エネルギーデバイス用半導体を追加、IV章にSiのウェットエッチングおよび最新の超微細加工技術を追加、その他ミスプリントを修正した。 2012年10月

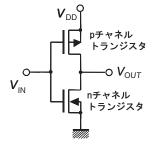

- ・CMOS インバータと細線効果の図面および p チャネルトランジスタのしきい値電圧の式を追加、その他ミスプリントを修正した。 2013 年 10 月

- ・索引を追加した。その他ミスプリントを修正した。

- 2014年10月

- ・コラムを 3 件、酸化速度の不純物濃度依存性、PMA、NAND のレイアウト図、レジスト剥離法などを 追加した。表 II.1 に  $Si_3N_4$  を追加、その他ミスプリントを修正した。 2015 年 10 月

- ・コラムを1件、CMOSの製作工程図、本研究所のSi酸化速度の図、酸化速度の不純部濃度依存性の図、SiO2とレジスト中のイオンの射影飛程と分散の図、イオン注入後アニールした時の不純物分布関数に関する記述を本文中に追加した。また、付録に真空準位に関する解説と周期表を追加した。その他ミスプリントを修正した。 2016年10月

- ・チャネル長変調効果を追記した。一部の説明を改訂した。ミスプリントを修正した。 2017年10月

また、2017年改訂版の作成にあたり、丁寧に本書を熟読しミスプリントを指摘していただいた広島 大学ナノデバイスバイオ融合科学研究所研究員山田真司氏に感謝申し上げます。

著者識

## 目 次

| 緒 | 言       |                                                                     |    |

|---|---------|---------------------------------------------------------------------|----|

|   |         | の歴史                                                                 |    |

|   | I • 1   | LSI とは・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                          | 1  |

|   | I • 2   | トランジスタ・LSI の発明 · · · · · · · · · · · · · · · · · · ·                | 1  |

|   | I • 3   | LSI の進歩・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                         | 2  |

|   | I • 4   | ムーアの法則                                                              | 3  |

|   | 問題      | į I                                                                 | 3  |

| Ι | I 半     | 導体の基礎                                                               |    |

|   | II • 1  | 半導体とは・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                           | 4  |

|   |         | <ul><li>・シリコン半導体・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>      | 4  |

|   | II • 2  | エネルギーバンドと電気伝導・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   | 5  |

|   |         | <ul><li>エネルギーバンドの形成機構・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul> | 5  |

|   |         | ・バンドギャップの大きさによる物質の分類                                                | 7  |

|   |         | ・エネルギーバンドと電気物性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  | 8  |

|   |         | ・直接遷移型および間接遷移型半導体・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・               |    |

|   | II • 3  | 分布関数と状態密度・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       |    |

|   |         | ・電子の分布関数                                                            | 9  |

|   |         | ・状態密度の計算・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                        | 10 |

|   |         | <ul><li>・低次元系のメリットを生かしたデバイスの例(量子井戸レーザ)</li></ul>                    | 13 |

|   | II • 4  | 半導体中の電子および正孔密度・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  | 15 |

|   |         | ・真性半導体中の電子および正孔密度                                                   | 15 |

|   |         | <ul><li>実際の半導体の伝導電子の等エネルギー面・・・・・・・・・・・・</li></ul>                   | 16 |

|   |         | ・外因性半導体中の電子および正孔密度                                                  | 17 |

|   |         | <ul><li>外因性半導体中のフェルミレベルとキャリア密度</li></ul>                            | 17 |

|   |         | <ul><li>縮退半導体について・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>       |    |

|   | II • 5  | 電子、正孔の輸送機構・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      |    |

|   |         | <ul><li>・ドリフト電流・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>       | 20 |

|   |         | ・半導体の抵抗率・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                        | 22 |

|   |         | • 拡散流 · · · · · · · · · · · · · · · · · · ·                         |    |

|   |         | ・電流密度の式・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                         |    |

|   |         | <ul><li>キャリア連続の式・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>      | 23 |

|   |         | ・ポアソン方程式                                                            |    |

|   |         | ・擬フェルミ準位 (Imref)                                                    |    |

|   | II • 6  | 1 4 11 1 21 2005                                                    |    |

|   |         | Î II                                                                |    |

|   |         | .1: n型、p型半導体の説明図・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 26 |

| Ι |         | OS トランジスタの物理                                                        |    |

|   | III • 1 | p-n 接合 · · · · · · · · · · · · · · · · · ·                          |    |

|   |         | • p-n 接合の形成方法・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |    |

|   |         | • p-n 接合の電流-電圧特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |    |

|   |         | ・トンネルダイオード (エサキダイオード)                                               |    |

|   |         | • p-n 接合の降伏現象 · · · · · · · · · · · · · · · · · · ·                 | 34 |

|         | ・省エネルギーデバイス用半導体 · · · · · · · · · · · · · · · · · · ·               | 35 |

|---------|---------------------------------------------------------------------|----|

|         | 例題 III. 1· · · · · · · · · · · · · · · · · · ·                      | 35 |

| III • 2 | MOS 構造 · · · · · · · · · · · · · · · · · ·                          | 36 |

|         | 例題 III. 2·····                                                      | 39 |

|         | ・MOS 構造の容量-電圧特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 | 39 |

| III • 3 | MOS トランジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 42 |

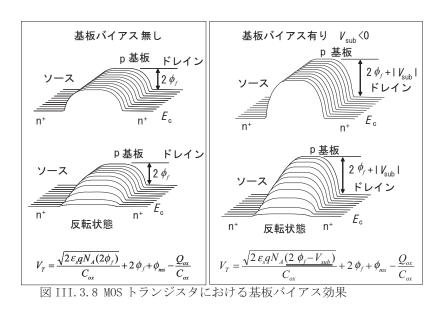

|         | <ul><li>・基板バイアス効果・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>      | 44 |

|         | ・MOSIC の特徴・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 44 |

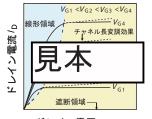

|         | <ul><li>MOS トランジスタの電流ー電圧特性</li></ul>                                | 45 |

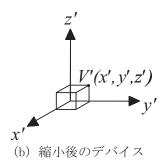

| III • 4 | スケーリング則・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                         | 45 |

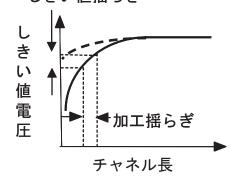

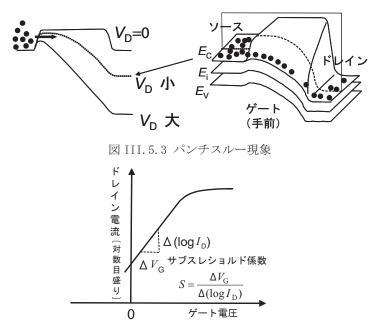

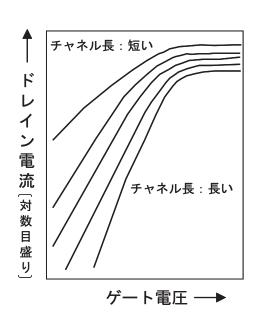

| III • 5 | 微細化に伴う諸現象・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       | 48 |

|         | <ul><li>・短チャネル効果・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>      | 48 |

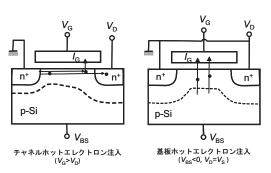

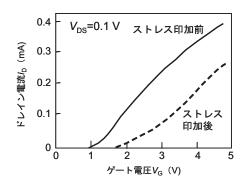

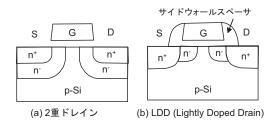

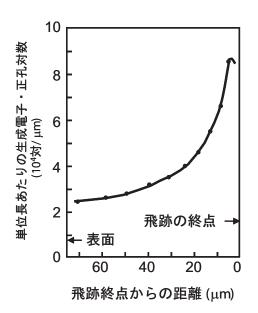

|         | <ul><li>・ホットキャリア発生抑制法・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul> | 50 |

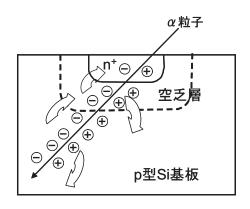

|         | <ul><li>ソフトエラー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>        | 51 |

|         | <ul><li>・微細化に伴うその他の諸現象・・・・・・・・・・・・・・・・</li></ul>                    | 51 |

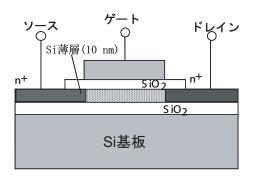

|         | <ul><li>・微細化諸問題を克服するトランジスタ構造の例・・・・・・・・・・・・・・・</li></ul>             | 52 |

| 問題      | [III                                                                | 53 |

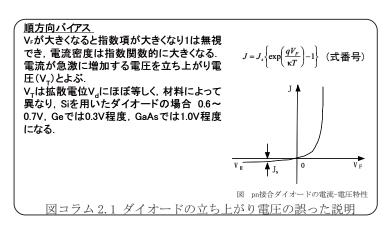

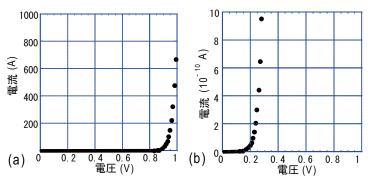

| コラム2    | 2: ダイオードの立ち上がり電圧                                                    | 54 |

| IV LSI  | の製作プロセス                                                             |    |

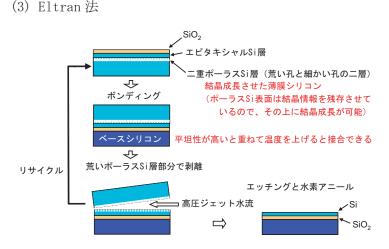

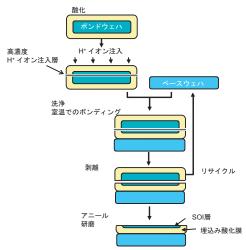

| IV • 1  | Si ウェハ製作工程・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 55 |

| IV • 2  | LSI 製作工程 · · · · · · · · · · · · · · · · · · ·                      | 56 |

|         | ・CMOS 作製工程・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 58 |

|         | <ul><li>プレーナ技術・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>                    | 60 |

|         | <ul><li>自己整合技術・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>        | 60 |

| IV • 3  | リソグラフィ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                          | 61 |

| IV ·    | • 3-1 フォトリソグラフィ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 | 61 |

| = :     | ・3-2 電子ビームリソグラフィ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 64 |

|         | ・3-3 ナノインプリントリソグラフィ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             | 66 |

|         | ・3-4 レジスト・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       | 66 |

| IV ·    | ・3-5 クリーンルームの必要性                                                    | 67 |

|         | エッチング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                           | 68 |

|         | • 4-1 ウェットエッチング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 | 70 |

| IV ·    | · 4-2 ドライエッチング······                                                | 71 |

|         | · 4-3 セルフバイアス······                                                 | 72 |

|         | · 4-4 チャージアップダメージ······                                             | 74 |

| IV ·    | • 4-5 エッチングガスによる環境問題                                                | 75 |

| IV ·    | · 4-6 難エッチング材料の加工法(リフトオフ法)                                          | 76 |

|         | <ul><li>・レジストの除去方法・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</li></ul>    | 76 |

| _ :     | ・4-7 最新の超微細加工技術・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 |    |

| IV • 5  | 薄膜形成 · · · · · · · · · · · · · · · · · · ·                          | 79 |

| IV ·    | •5-1 Chemical Vapor Deposition (CVD: 化学気相堆積法) ······                | 80 |

| IV ·    | • 5-2 Si 熱酸化膜                                                       |    |

|         | • 犠牲酸化······                                                        |    |

| IV ·    | ・5-3 Deal Grove の酸化モデル・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・          | 84 |

| • 酸·       | 化速度の不純物濃度依存性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 86  |

|------------|-----------------------------------------------------------------|-----|

| IV • 5-4   | スパッタリング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | 86  |

| IV • 5-5   | 高誘電体、強誘電体膜の形成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・               | 89  |

| IV·6 不純    | 物ドーピング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 90  |

|            | 例題 IV. 1- · · · · · · · · · · · · · · · · · ·                   | 92  |

| IV • 6-1   | 熱拡散法 · · · · · · · · · · · · · · · · · · ·                      | 93  |

| IV • 6-2   | イオン注入                                                           | 96  |

| IV • 6-3   | 不純物の再分布・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | 101 |

| IV•7 配線    |                                                                 | 103 |

| IV • 7-1   | 金属配線の信号遅延・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   | 103 |

| • LS       | I 長距離配線におけるリピータ                                                 | 105 |

| IV • 7-2   | 配線におけるスケーリング則                                                   | 106 |

| IV • 7-3   | 配線のプロセスコスト                                                      | 107 |

| IV • 7-4   | 金属配線材料・シリサイド・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 108 |

| IV • 7-5   | エレクトロマイグレーション                                                   | 109 |

| IV • 7-6   | ストレスマイグレーション・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 111 |

| IV • 7-7   | Al と Si の反応 (共晶の形成)                                             | 112 |

| • Pos      | st Metallization Anneal (PMA)                                   | 113 |

| IV • 7-8   | 化学的機械研磨技術(Chemical Mechanical Polish: CMP)・・・・・・・               | 115 |

| IV • 7-9   | 金属のメッキ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 117 |

| IV • 7-10  | 0 光配線                                                           | 117 |

| 問題 IV···   |                                                                 | 122 |

| コラム 3: MC  | SFET 試作失敗談                                                      | 123 |

| V LSI の将   |                                                                 |     |

| V・1 サイフ    | 《限界                                                             | 125 |

| • i 5      | 型半導体内の電位分布・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  | 131 |

|            | 産延・発熱                                                           |     |

| V・3 速度・    | 電力 · · · · · · · · · · · · · · · · · · ·                        | 132 |

| · ス        | イッチング速度                                                         | 133 |

| · ス        | イッチングエネルギーの量子力学的極限‥‥‥‥‥‥‥‥‥                                     |     |

| · ス        | イッチングエネルギーの熱力学的極限 ‥‥‥‥‥‥‥‥‥‥                                    | 135 |

| • <b>Z</b> | イッチングエネルギーの熱放散極限‥‥‥‥‥‥‥‥‥‥                                      | 135 |

| V・4 今後の    | ) LSI                                                           | 135 |

| ・シ         | ステム LSI・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | 138 |

| 問題 V····   |                                                                 | 141 |

| コラム 4: 短   | 期 CMOS 回路作製挑戦記                                                  | 142 |

|            | 皇事項)                                                            |     |

|            | - ・ へ)<br>三次元空間でのドリフト電流式の導出・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |     |

| 付録 I・2 n   | i-p-n 接合における障壁高さの p 層膜厚依存性 (パンチスルー効果)・                          | 146 |

|            | 大陥密度・歩留関係式の導出・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・               |     |

|            | 下純物数の揺らぎとしきい値電圧・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             |     |

|            | 真空準位について                                                        |     |

|            | 頃と解答)・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       |     |

|            |                                                                 |     |

|            |                                                                 |     |

| 付録 | : IV  | 周 | 期   | 表 | <br> | <br>  | • |   | ٠. |      | ٠. |       | ٠. |      | ٠. | • |    | ٠. |      | ٠. | <br> |   |   |      | <br>٠. | <br> | <br>  | • | <br>٠. | ٠. | <br>1 | 54 |

|----|-------|---|-----|---|------|-------|---|---|----|------|----|-------|----|------|----|---|----|----|------|----|------|---|---|------|--------|------|-------|---|--------|----|-------|----|

| 参考 | 文南    | 犬 | • • |   | <br> | <br>• |   |   |    | <br> |    | <br>  |    | <br> |    |   | ٠. |    | <br> |    | <br> |   | • | <br> |        | <br> | <br>• |   |        |    | <br>1 | 55 |

| 索引 | • • • |   |     |   | <br> | <br>  |   | • |    |      |    | <br>• |    |      |    |   | •  |    |      |    | <br> | • |   | <br> |        | <br> |       |   |        |    | <br>1 | 56 |

| 欧文 | 索引    |   |     |   | <br> |       |   |   |    | <br> |    | <br>  |    | <br> |    |   |    |    | <br> |    | <br> |   |   | <br> |        | <br> |       |   |        |    | <br>1 | 63 |

## I. LSI の歴史

## I・1 LSIとは

LSI とは Large Scale Integrated Circuit または Large Scale Integration のことであり、直訳すると大規模集積回路である。図 I.1.1 に示すように、LSI は身近なパーソナルコンピュータ(パソコン)やゲームマシンの Central Processing Unit (CPU) やメモリなどとして使用されている。LSI は、図 I.1.2 に示すように情報社会のあらゆる製品に使用されており、いまや LSI なしに文明社会は成立しないため、産業の米と言われている。

図 I.1.1 LSI はどこに使われているか

PC: Personal Computer PDA: Personal Digital Assistant GPS: Global Positioning System EC: Electronic Commerce 電子商取引

図 I.1.2 情報社会における LSI の用途

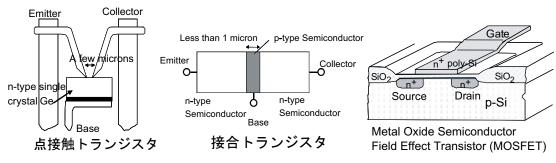

## I・2 トランジスタ・LSI の発明

LSI を構成している最も重要な部品は、トランジスタである。トランジスタの語源は、transfer(運ぶ)resistor(抵抗器)、すなわち電気信号を増幅する固体素子である。それまでの真空管に代わる固体信号増幅素子の開発中に、1947年にアメリカ Bell 研究所の Bardeen,Brattain,Schockley の3名によって点接触トランジスタが発明され、後にノーベル賞を受賞している。図 I.2.1にトランジスタの進歩を示す。点接触トランジスタは不安定で実用にならず、その後接合トランジスタが発明され実用化された。現在は、接合トランジスタより低消費電力で高集積化が可能な MOS 電界効果トランジスタ (Metal Oxide Semiconductor Field Effect Transistor: MOSFET) が主流である。

図 I.2.1 トランジスタの進歩

トランジスタの発明後しばらくは、トランジスタ、ダイオード、抵抗、コンデンサなどの電子部品を、プリント基板に半田付けによって実装して電子製品が製作されていたが、1958年にアメリカテキサスインスツルメンツ社の Jack Kilby (2005年没)によって、これらの電子部品を一枚の半導体基板上に一括して作りつける「集積回路」が発明され、2000年にノーベル賞を受賞した。これより半年遅れて、フェアチャイルド・セミコンダクター社の Robert Noyce によって、現在のものにより近い集積回路が独自に発明されていたが、1990年に他界したため、ノーベル賞受賞は逸している。図 I.2.2に Kilby 氏と彼が最初に製作した集積回路の写真を示す。集積回路の発明によって、電子機器の信頼性は、それまでの半田付けに頼っていたものに比べ格段に向上し、電子システムとしての機能も知能LSIができるほどに向上した。

図 I.2.2 Jack Kilby 氏と最初 に製作された集積回路

## I・3 LSI の進歩

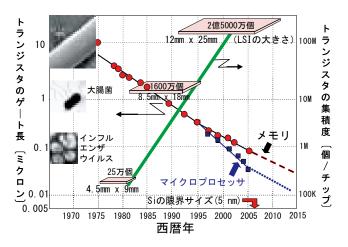

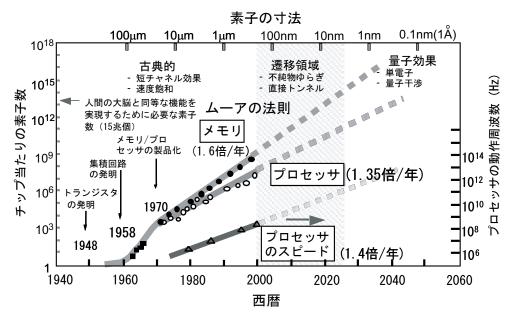

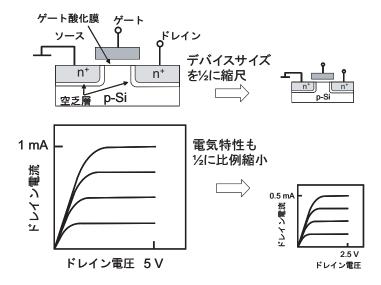

トランジスタの微細化と、これによるLSIの進歩の様子を図 I.3.1 と図 I.3.2 に示す。この 30 年間で、素子サイズは1/100(0.7 倍/3 年) に、1つのチップ上に集積される素子数は約 100 万倍に大規模化した。また、クロック周波数は 15 年間で約 100 倍以上になった。

図 I.3.1 トランジスタの微細化

図 I.3.2 LSI の進歩

### Ⅰ・4 ムーアの法則

図 I.3.2 から分かるように、1.5 年から 2 年で、チップ当たりのトランジスタ数が倍になってきた。ゴードン・ムーア (Gordon Moore) は、1965 年にこのことに気づき、この傾向が持続すると予測した。この経験則をムーアの法則 (Moore's law) と呼ぶ。ムーアの法則は、次の 2 つの牽引力によって達成されてきた。

- (1) トランジスタの微細化 (3年で0.7倍→3年で2倍の集積度向上)

- (2) チップ面積の増大(3年で2倍の面積増大が必要)

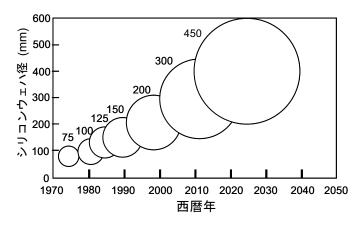

括弧内の数字は、チップ上のトランジスタ数が 1.5 年で 2 倍に増すものとした時の値である。チップ 面積が増大すると、ウェハ当たりのチップ収量が減少し、チップ単価が上昇する。この問題を解決するため、素子の微細化と同時にウェハの大口径化が行われてきた。その様子を図 I.4.1 に示す。最新 の量産ラインでは 300mm 直径のウェハが使用されている。

図 I.4.1 ウェハ大口径化の様子

#### 問題 I.

- (1)「個別デバイスを半田付けして製作した電子システム」と集積回路とを比較せよ。

- (2) 素子を微細化するメリットを説明せよ。

- (3) シリコンウェハを大口径化する理由を説明せよ。

- (4) ムーアの法則とは何か説明せよ。

## II. 半導体の基礎

## Ⅱ・1 半導体とは

LSI は半導体から作られるので、半導体の基礎事項を復習しておく。

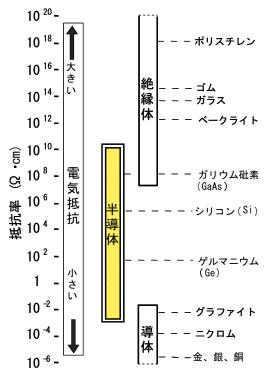

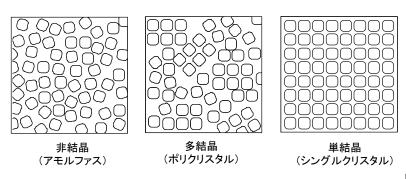

半導体は、絶縁体と導体の中間の性質を持った物質である。半導体の性質(例えば電気抵抗)は、電界、温度、圧力、不純物など、環境によって敏感に変化するため、電子デバイスに広く応用される。図 II.1.1 に様々な物質の抵抗率(比抵抗)を示した。代表的な半導体には、シリコン(Si)、ゲルマニウム(Ge)、ガリウム砒素(GaAs)などがある。同じ半導体でも、原子の集合状態によってその性質は大きく変化する。図 II.1.2 は物質の3つの状態を示す。原子が整然と規則正しく並んだものが単結晶(Single Crystal)、小さな単結晶粒がランダムに集合したものが多結晶(Poly-crystal)、規則性のないものが非晶質(Amorphous)である。単結晶は、電子やホールの移動度が最も大きくなるので、

図 II.1.1 色々な物質の電気抵抗率

高性能電子デバイスに用いられる。非晶質は低コストで 大面積が必要なアモルファス Si (a-Si) 太陽電池などに 用いられる。

#### ・シリコン半導体

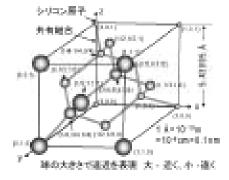

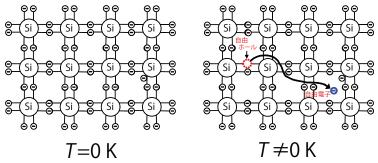

図 II.1.3 は、現在の LSI の基板として用いられている Si 単結晶の基本格子(ダイヤモンド構造)を示す。面心立方格子を、立方体の対角線方向に 1/4 周期ずらしたものを 2 つ重ねた構造である。単位胞中に正味含まれる Si 原子は 8 個であり、原子密度は 5.0x $10^{22}$  個 /cm³、密度は 2.33g/cm³ で A1 (2.69g/cm³) に比べ少し小さい。 Si は周期表第 IV 族の元素で、4 つの最外殻電子を持ち、sp3 混成軌道による共有結合物質である。2 次元の結晶模式図を図 II.1.4 に示す。不純物の無い純粋な Si (真性 [i型] 半導体と言う)では、温度 T=0K の時は、電流を担うキャリアは無く、電気抵抗は無限大である。温度が上昇すると共有結合の一部が切れ、自由に動き回ることのできる電子と、その抜け穴である正孔(ホール)が

図 II.1.2 原子の集合状態による物質の分類

図 II.1.3 Si 単結晶の基本格子(ダイヤモンド構造)

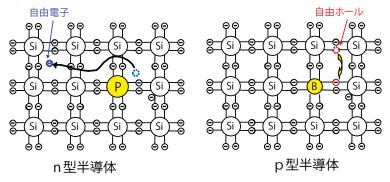

キャリアとなり、電気抵抗が減少する。図 II. 1.5 に示すように、V 族または III 族の不純物原子を、結晶格子の一部に置換する(不純物ドープ)と、自由に動き回れる電子またはホールが生成され、電気抵抗が不純物量によって制御できる。V 族元素をドーピングして電子がキャリアとなるものを n型半導体、III 族元素ドーピングよってホールがキャリアとなるものを p型半導体と呼ぶ。

図 II.1.4 Si 単結晶真性半導体の電気伝導

図 II.1.5 Si 単結晶に不純物をドープした場合の電気伝導

## II・2 エネルギーバンドと電気伝導

#### ・エネルギーバンドの形成機構

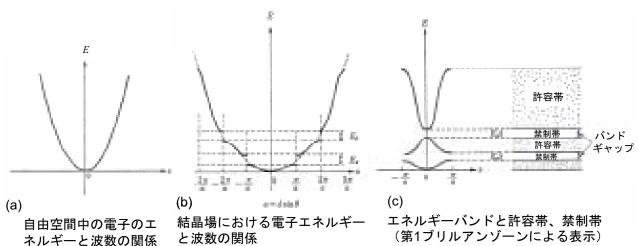

結晶中の電子のエネルギーは、図 II. 2.1(c) に示すように、離散的な複数の帯 (エネルギーバンド) に分かれている。エネルギーバンドが形成される理由として、次の2種類のモデルがある。

- (1) 自由電子近似モデル (結晶周期場に自由電子を入れるモデル)

- (2) 束縛電子近似モデル (孤立原子を近づけていって、結晶になったときを考えるモデル)

- (1) 自由電子近似の考え方を図 II. 2.1 に示す。自由空間(真空中)における電子の波数  $k(k=2\pi/\lambda,\lambda)$  は波長)とエネルギーEの関係は、 $E=\hbar^2k^2/2m$  で与えられ(mは電子の質量、 $\hbar=h/2\pi$  ,  $\hbar$  はプランク定数)、図 II. 2.1(a) の様に放物線になる。一方、結晶中では、電子波は格子原子によって散乱され、次のブラッグ回折の条件を満たす時、散乱波は強め合って強く反射される。

図 II. 2.1 自由電子近似によるエネルギーバンド形成モデル

ブラッグの回折条件  $2d\sin\theta = n\lambda$

$(II \cdot 2 \cdot 1)$

入射、反射波の行路差= $2d\sin\theta$

ここに、d は格子周期、 $\theta$  は電子の結晶面に対する入射角、 $\lambda$  は電子の波長、n は整数である。 簡単のため 1 次元結晶を考える。ブラッグ回折の結果、次式に示すように、進行波(入射波)と反射 波の干渉によって定在波が生じる。

$$\sin \omega (t - x/v) + \sin \omega (t + x/v) = 2 \sin \omega t \cdot \cos \omega x/v$$

$$= 2 \sin \omega t \cdot \cos (kx)$$

(II. 2. 2)

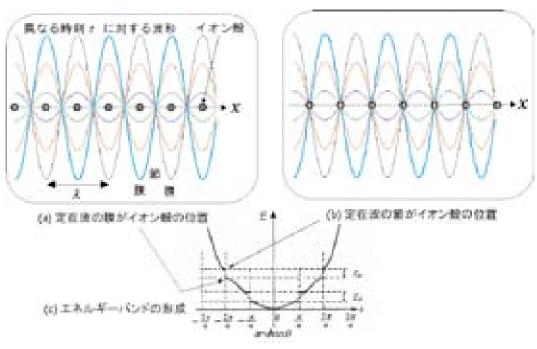

ここで、v は速度、 $k = \omega/v = 2\pi/\lambda$ 。図 II. 2. 2(a) に示すように、定在波の腹が陽イオン殻の位置に一致する場合、系のエネルギーが最も低くなる(電子波の振幅の二乗が電子の存在確率になることに注意)。一方、定在波の節が陽イオン殻の位置に一致すると(図 II. 2. 2(b))、系のエネルギーは最も高くなる。上記 2 つの中間の位置に、定在波が安定に位置することはない。なぜなら、電子と陽イオン殻間のクーロン引力により、どちらかのつりあいの位置に移動するためである。このように、ブラッグ回折の起こる波数において、電子のエネルギーは高低 2 つに分離し、図 II. 2. 2(c) または図 II. 2. 1(b) に示すように禁制帯と許容帯が生じる。図 II. 2. 1(c) は、波数領域を $-\pi/a \le k \le \pi/a$  (ここに  $a = d \sin \theta$ ) の第 1 ブリルアンゾーンに限定した表示である。このように  $k \in 2\pi/a$  の整数倍ずらしても良いのは、結晶場における電子の波動関数が、k の  $2\pi/a$  の整数倍の変化に対して不変のためである。

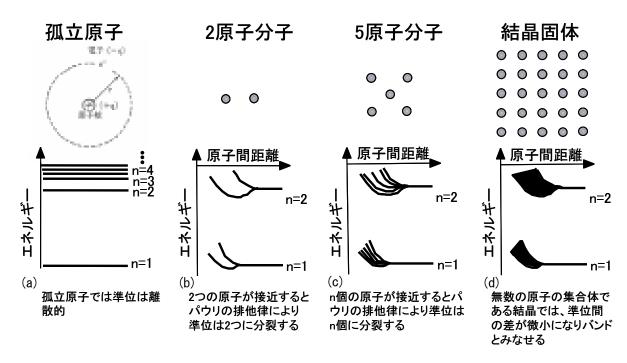

(2) 束縛電子近似の考え方を図 II. 2. 3 に示す。孤立原子における電子エネルギーは図 II. 2. 3(a) に示すように、量子数に応じて離散的な値をとる。一つのエネルギー準位には、スピンの異なる 2 個の電子しか存在できない(パウリの排他律)。図 II. 2. 3(b), (c) に示すように複数の原子が近づいて分子を形成する場合を考える。原子が数 nm 以下に接近して原子間に相互作用が生じると、同じエネルギーの準位に 2 個以上の電子は存在できないので、エネルギー準位が分裂し、異なるエネルギーをとることによってパウリの排他律を満足するようになる。大雑把には、より集まった原子の数だけ、エネル

図 II. 2.2 定在波によるエネルギーギャップ (禁制帯) の形成

図 II. 2.3 束縛電子近似によるエネルギーバンド形成のモデル

ギーが分裂する。結晶固体、たとえば  $1 \text{cm}^3$  の Si 単結晶では、 $5 \text{x} 10^{22}$  個もの原子が集合し、お互いに相互作用しあっているので、エネルギー準位は  $5 \text{x} 10^{22}$  個に分裂し、準連続の帯すなわちエネルギーバンドを形成する(図 II.2.3(d))。すなわち、孤立原子の量子準位が結晶固体になると幅をもつ結果、エネルギーバンドが形成される。エネルギー(バンド)ギャップは、孤立原子の量子準位が離散的であったことの痕跡とみなすことができる。

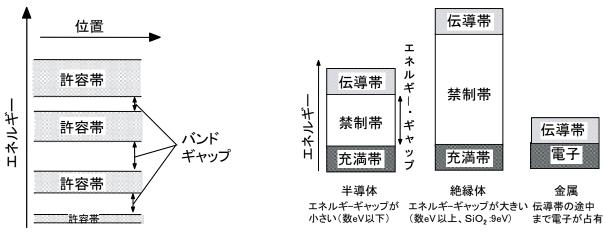

#### ・バンドギャップの大きさによる物質の分類

結晶の簡略化したエネルギーバンド図を図 II.2.4 に示す。電子で一杯に詰まった許容帯を充満帯と呼ぶ。電子で充満されていない最上部のバンドを伝導帯と呼ぶ。充満帯のうち原子の結合にあずかる価電子で構成されるものを価電子帯と呼ぶ。充満帯の電子は電気伝導に寄与しない。電流が流れるためには、電界によって電子が加速され高いエネルギー準位に移らねばならない。しかし、充満帯には空いた準位がないので、電子を充満帯にとどめたまま加速することができない。電気伝導を担うのは、伝導帯の電子、および充満帯の電子が抜けてできた孔、即ち正孔(またはホール)である。ホールは正の電荷を持つ擬似粒子とみなすことができる。絶縁体、半導体、金属の違いをエネルギーバンドによって説明すると図 II.2.5 のようになる。半導体はバンドギャップが比較的小さく(0.1-数

図 II. 2.4 簡略エネルギーバンド図 図 II. 2.5 バンドギャップの大きさと物質

eV)、室温の熱エネルギーによって、価電子帯から伝導帯に電子が熱励起され得る。絶縁体はバンドギャップが数 eV以上で、通常の環境下では電気伝導性は非常に低く電気絶縁用として使用される。 金属は伝導帯が途中まで電子で満たされていて、極低温まで電気伝導性が高い。その他に半金属と呼ばれる、伝導帯と価電子帯が一部重なっているものもあるがここでは省略する。

#### ・エネルギーバンドと電気物性

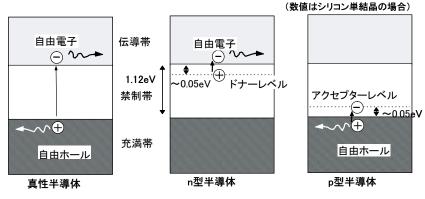

図 II. 1. 4, II. 1. 5 に示した 3 種類の半導体(真性 [i 型]、n 型、p 型)をエネルギーバンドを用いて説明すると図 II. 2. 6 のようになる。

- (1) 真性半導体では、熱エネルギーによって充満帯(価電子帯)から伝導帯に励起された電子と価電子帯に生成されたホールが電流を運ぶ。

- (2) n 型半導体では、ドープした V 族不純物原子によってバンドギャップ中の伝導帯底付近にドナーレベル(電子を供与するのでドナーと言う)が形成され、熱エネルギーによってドナーレベルから伝導帯に電子が励起され電気伝導に寄与する。正にイオン化したドナーは自由に動き回ることができないので伝導には寄与せず空間電荷をつくる。

- (3) p型半導体では、Ⅲ 族原子によってバンドギャップ中の価電子帯頂上付近にアクセプターレベル(電子を受け 入れるのでアクセプターと言う)が形成され、価電子帯からアクセプターレベルに電子が熱励起されることに よって形成されるホールがキャリアとなる。負にイオン化したアクセプターもドナーと同様空間電荷となる。

#### 直接遷移型および間接遷移型半導体

図 II.2.7 に直接遷移型と間接遷移型半導体のバンド構造を示した。直接遷移型半導体では、伝導帯の底と価電子帯の頂上が同じ波数に位置する。これに対し、間接遷移型半導体では、それらが異なる波数の所に位置する。両者の物性の大きな違いは光学特性にある。直接遷移型半導体では、電子・

図 II. 2.6 真性、n型、p型半導体のエネルギーバンド図

図 II.2.7 直接遷移型および間接遷移型半導体

正孔再結合が同じ波数で起こるの で、格子振動(フォノン)を介さ ずに遷移し、遷移確率が高く発 光効率が高い。このため、直接遷 移型である GaAs や GaN は発光ダ イオード (LED: Light Emitting Diode) や半導体レーザとして用 いられている。一方、間接遷移型 の場合は、電子・正孔再結合が異 なる波数で起こるので、運動量保 存則を満たすためにフォノンを介 した遷移が必要である。そのため、 遷移確率が低く発光効率が低いた め発光素子には適さない。Geや LSI に使用される Si は間接半導 体であり、発光デバイスとしては 適さない。しかし、最近、Si量 子ドット、Si 超薄膜、Si のラマ ン効果を利用した発光デバイス、 ヘビードープ歪み Ge など、発光 効率を向上させる研究が進んでい る。

## Ⅱ・3 分布関数と状態密度

半導体の電気伝導度σは次式によって決まる。

$$\sigma = qn\mu_n \mathcal{E} + qp\mu_p \mathcal{E} \tag{II-3-1}$$

ここに、q は電子電荷 (q=1.602x10 $^{-19}$ C)、n, p はそれぞれ電子及び正孔の密度、 $\mu_n$ ,  $\mu_p$  はそれぞれ電子及び正孔の移動度、 $\varepsilon$  は電界強度である。n 及びp は次式で与えられる。

$$n = \int_{E_C}^{\infty} N_C(E) f(E) dE$$

(II· 3· 2)

$$p = \int_{-\infty}^{E_V} N_V(E) (1 - f(E)) dE$$

(II· 3· 3)

ここに、 $N_c(E)$  は電子の状態密度で、単位体積の物質中、単位エネルギー幅内に存在する電子を収容できるエネルギー準位の数である。f(E) は電子の分布関数で、エネルギー幅  $(E, E+\Delta E)$  における電子の存在確率が $f(E)\Delta E$  であることを意味する。 $N_v(E)$  は正孔の状態密度、1-f(E) は正孔の分布関数である。電子及び正孔の移動度  $\mu_n$ ,  $\mu_p$  は、用いられる半導体の性質と、温度、不純物濃度、結晶欠陥密度などによって決まる。

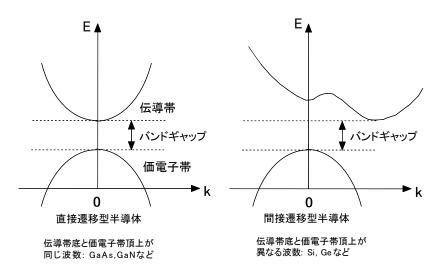

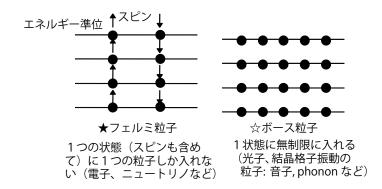

#### 電子の分布関数

電子の分布関数f(E)は、次のフェルミ・ディラック(またはフェルミ)分布関数で与えられる。

$$f(E) = \frac{1}{1 + \exp\left(\frac{E - E_F}{kT}\right)}$$

(II· 3· 4)

ここで、 $E_F$ はフェルミエネルギーで、 $f(E_F)=1/2$ となる。kはボルツマン定数 ( $k=1.38 \times 10^{-23} \text{ J/K}$ )、Tは温度 (K) である。f(E) の概略を図 II. 3.1 に示す。フェルミ・ディラック分布関数に従う粒子をフェルミ粒子と呼び、電子のほかにニュートリノなどがある。この分布関数は、1 つのエネルギー準位にスピンの異なる 2 つの粒子しか入れないとして統計理論から導かれる。一方、1 エネルギー準位に無制限に入れる粒子をボース粒子と呼び、光子、結晶格子振動の粒子(フォノン)などがある(図 II. 3.2)。 参考:ボース粒子の分布関数は、次のボース・アインシュタイン分布関数で与えられる。

$$f(E) = 1/(\exp((E - E_E)/kT) - 1)$$

エネルギーが大きく、 $E-E_F$ >>kT, E>> $E_F$  の場合は、フェルミ・ディラック分布関数もボース・アインシュタイン分布関数も共に、次のボルツマン分布関数で近似される。

$$f(E) \propto \exp(-E/kT)$$

(II· 3· 5)

図 II.3.1 フェルミ・ディラック分布関数

図 II.3.2 フェルミ粒子およびボース粒子

#### 状態密度の計算

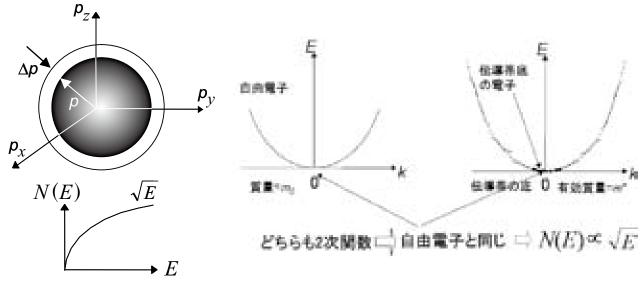

電子の状態密度 N(E) は、単位体積の物質において、エネルギー幅  $(E,E+\Delta E)$  において存在できる電子の数が  $N(E)\Delta E$  として定義される。 1 つのエネルギー準位をスピンの異なる 2 個の電子が占有できるので、エネルギー準位の数としては  $N(E)\Delta E$  /2 である。簡単のため 1 次元で考える。長さ  $L_x$  の物質中に閉じ込められた電子の運動量  $p_x$  の不確定性  $\Delta p_x$  は、ハイゼンベルクの不確定性より、 $\Delta p_x \cdot L_x \sim h$  と表せる。ここに、h はプランク定数である。この式の意味は、電子の運動量状態は、 $\Delta p_x$  の刻みより細かく区別することはできない、逆に言うと運動量空間における状態の最小ユニットは  $\Delta p_x$  ということができる。同様に、三次元の運動量空間において、 $\Delta p_x \Delta p_y \Delta p_z \sim h^3/L_x L_y L_z$  が状態の最小ユニットとなる。単位体積の物質を考えると  $L_x L_y L_z = 1$  の故、 $\Delta p_x \Delta p_y \Delta p_z \sim h^3$  に 1 つの状態が割り当てられる(図 II.3.3)。このことを基本に、3 次元、2 次元、2 次元、および 1 次元電子の状態密度を計算する。

図 II.3.3 運動量空間における状態の最小ユニット

### (1) 3次元電子の状態密度

$$E = p^{2}/2m = (p_{x}^{2} + p_{y}^{2} + p_{z}^{2})/2m$$

(II. 3. 6)

従って、エネルギーE一定の領域は運動量空間では球面になる(図II.3.4)。

$(E, E+\Delta E)$  領域は、運動量空間では  $(p, p+\Delta p)$  の球殻に対応する。

従って、 $(E, E+\Delta E)$  領域における状態数  $N(E)\Delta E$  は、 $(p, p+\Delta p)$  の球殻における状態数に等しい。 故に、スピンを考慮して(1 エネルギー準位に2 個の電子が存在)  $N(E)\Delta E=2\times 4\pi p^2\Delta p/h^3$  (II· $3\cdot7$ ) 一方、 $E=p^2/2m$  より、 $\Delta E=2\pi\Delta p/2m$  (II· $3\cdot8$ )

(II·3·8) を (II·3·7) に代入すると、

$$N(E)2\pi\Delta p/2m = 8\pi p^2 \Delta p/h^3 \rightarrow N(E) = 8\pi pm/h^3$$

(II. 3. 9)

(II·3·6) より p=(2mE)<sup>1/2</sup> を (II·3·9) に代入し、

$$N(E)=16\pi m^{2}(E/2m)^{1/2}/h^{3}$$

(II· 3· 10)

即ち、3次元自由電子の状態密度はエネルギーの1/2乗に比例する。半導体の伝導帯の底は、これに相当する(図II.3.5)。

図 II.3.4 3 次元自由電子の状態密度

図 II.3.5 伝導帯の底の電子の状態密度

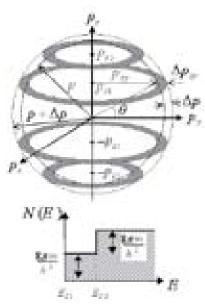

#### (2) 2次元電子の状態密度

$E=p^2/2m=(p_x^2+p_y^2+p_z^2)/2m$  (閉じ込め方向の $p_z^2/2m=E_m$ は量子化され離散化) 今、電子のエネルギー $E=p^2/2m$  は z 方向の 1 番目および 2 番目の量子化エネルギー $E_{z1}=p_{z1}^{-2}/2m$ , および $E_{x2}=p_{xx2}^{2}/2m$  よりは大きいが、3番目の量子化エネルギー $E_{x3}=p_{xx3}^{2}/2m$  よりは小さいとする。 この時、図 II. 3.6 に示すように、球面状の等エネルギー面が 4 つの平面  $p_{yz}$ =±  $p_{yz}$ 1, および  $p_{yz}$ =  $\pm p_{\chi r}$ と交わってできる 4 つの円周部分が許される状態となる。エネルギー範囲  $(E, E + \Delta E)$  にお いて許される状態は図中の灰色で示した4つの帯状円環部分となる。

まず、 $p_{xz}=p_{xz1}$  における帯状円環部分における状態数  $N(E)_{yz=yz1}\Delta E$  を計算する。

$$N(E)_{pz=pz1}\Delta E=2\pi p_{xy}\Delta p_{xy}/h^2$$

( $\Delta p_x\Delta p_y\sim h^2$  に 1 状態に注意) (II・3・12)

$$E=p^2/2m \ \ \, \downarrow \ \, 0 \ \, \Delta E=2p\Delta p/2m \tag{II} \cdot 3 \cdot 13)$$

また、図より

$$p_{xy}$$

= $p\cos\theta$ ,  $\Delta p_{xy}$ = $\Delta p/\cos\theta$  の故、  $p_{xy}\Delta p_{xy}$ = $p\Delta p$  (II·3·14)

(II·3·13) と (II·3·14) を (II·3·12) に代入すると、

$$N(E)_{pz=pz1} 2p\Delta p/2m = 2\pi p\Delta p/h^2 \rightarrow N(E)_{pz=pz1} = 2\pi m/h^2$$

(II· 3· 15)

これより、2次元自由電子の状態密度は $p_x, p_y$ によらず一定となることが分かる。

トータルの状態数 N(E) は、同様に計算し、更にスピンを考慮して(係数2をかけて)

$N(E) = \{N(E)_{pz=-pz1} + N(E)_{pz=-pz1}\} + \{N(E)_{pz=-pz2} + N(E)_{pz=-pz2}\} = 2 \times 4 \times 2\pi m/h^2 = 16\pi m/h^2$ となる。エネルギーを大きくしていくと、等エネルギー球面が次のz方向の量子化エネルギー 平面と交わり、新たなエネルギー状態が出現するので、N(E) は図 II.3.6 に示すように、段差 が  $8\pi m/h^2$  の階段状に変化する。

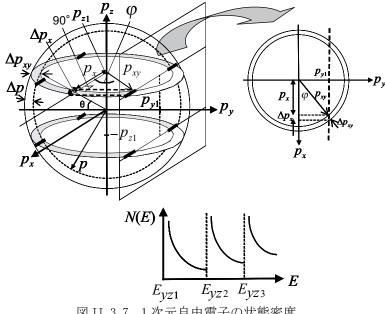

#### (3) 1次元電子の状態密度

$E=p^2/2$ m= $(p_x^2+p_y^2+p_z^2)/2m$  (閉じ込められるy, z方向のエネルギーは量子化)  $(II \cdot 3 \cdot 17)$ 球面状の等エネルギー面が 4 つの平面  $p_z=\pm p_{z1}, p_v=\pm p_{v1}$  と交わってできる 8 つの点状部分が許さ れる状態となる(図 II.3.7)。エネルギー範囲  $(E, E+\Delta E)$  において許される状態  $N(E)\Delta E$  は、図 中の黒色で示した8つの太い線分となる。

故に、

$$N(E)\Delta E=8\Delta p_x/h$$

( $\Delta p_x\sim h$  に 1 状態に注意、係数 8 は線分の数 ) (II· 3· 18)

$$E = (p_x^2 + p_y^2 + p_z^2)/2m$$

$(p_y p_z は一定) より、 $\Delta E = 2p_x \Delta p_x/2m$  (II·3·19)$

(II·3·19) を (II·3·18) に代入すると、 $N(E)=8m/(hp_x)=(8m/h)\{2m(E-E_{n,u})\}^{-1/2}$

図 II.3.6 2 次元自由電子の状態密度

図 II.3.7 1 次元自由電子の状態密度

ここに、 $E_{\upsilon,\mu}$  は y, z 方向の量子化エネルギー、 $\upsilon$ ,  $\mu$  は整数で、  $E_{\upsilon,\mu}$ =( $h^2/2m$ ) $\{(\upsilon\pi/L_y)^2+(\mu\pi/L_z)^2\}$

更にスピンを考慮して (2 倍して)、 $N(E)=(16m/h)\{2m(E-E_{nu})\}^{-1/2}$

$(II \cdot 3 \cdot 20)$

N(E) は図 II. 3.7 に示すような形になる。2 次元電子の時と同様に、エネルギーを大きくしていくと、等エネルギー球面が次の yz 方向の量子化エネルギー直線と交わり、新たなエネルギー状態が出現するので、(II·3·20) の形の関数が順次足し合わされていく。

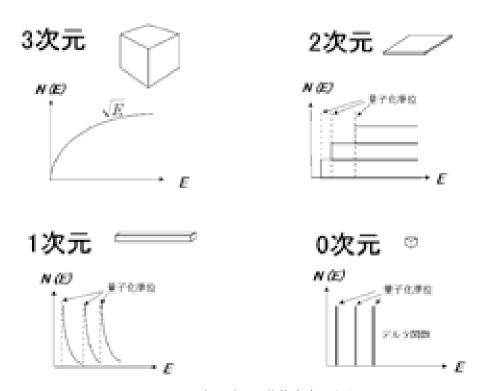

#### 状態密度のまとめ

3次元から0次元までの状態密度をまとめたものを図II.3.8に示す。各次元の電子系の特徴を以下に示す。特に最近は、微細加工技術の進歩により、低次元系の特徴を生かした電子デバイスの研究が盛んである。

- 3 次元系 キャリアの不純物散乱が大きい。GaAs 中の電子移動度~2x10<sup>5</sup>cm<sup>2</sup>/V·s (8K)

- 2 次元系特別な構造の工夫をすると散乱が抑制され移動度を極めて高くできる。GaAs 中の電子移動度 ~ 1x10<sup>6</sup>cm²/V·s (8K) HEMT (High Electron Mobility Transistor: 携帯電話の高周波デバイスとして使用されている)離散的な量子準位を利用した特殊なデバイス (負性抵抗素子など) ができる。

- 1次元系 2次元系に比べ散乱が抑制され移動度が極めて高い。 2次元系に比べ離散性の強い量子効果が現れる。ナノワイヤトランジスタに応用。

- **0 次元系** 1 次元系に比べ強い量子効果が現れ室温でも観測できる。キャリアを閉じこめることができる(量子ドットメモリ、量子ドットレーザ[発光効率の向上]など)。

図 II.3.8 3-0 次元電子の状態密度のまとめ

#### 低次元系のメリットを生かしたデバイスの例(量子井戸レーザ)

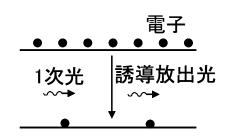

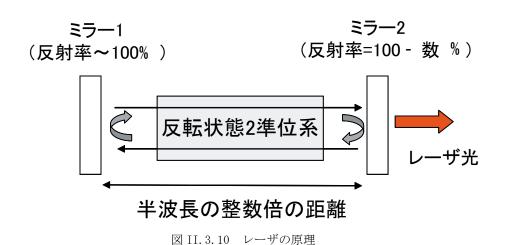

低次元系のメリットを生かしたデバイスの例として、レーザポインタなどに使われている、量子井戸レーザを紹介する。まず、簡単にレーザ (Laser) の原理を説明する。Laser は、Light amplification by stimulated emission of radiation の略である。直訳すると、「誘導放出による光増幅」となる。誘導放出とは、図 II. 3.9 に示すような反転状態(2 準位系において、エネルギーの高い方の準位の電子密度が、低い方の電子密度より大きい状態)が実現されている時、外部から 2 つの準位のエネルギー差にほぼ等しいエネルギーの光が入射すると、これに誘導されて(stimulated)電子遷移が起こり同じ波長の光が放出される(即ち光が増幅される)現象である。この系の両側に、反射率ほぼ 100% のミラーを、半波長の整数倍離して置く(図 II. 3.10)。すると光は、位相が揃うため、2 つのミラー間を往復するたびに増幅され(これを共振と呼ぶ)、2 準位系の増幅作用が飽和する光強度で飽和する。片方のミラーを数%光が透過するようにし、外部に取り出すエネルギー分を電気的、または別の光によって 2 準位系に補給して反転状態を維持することにより、定常的に光を取り出すことが可能となる。こうして得られた光は、ラジオ放送電波のように位相がきちんと揃い、外部に出てもあまり広がらない平行度の高い光となる。これがレーザ光線である。

反転状態の2準位系に、2準位のエネルギー差の光を入射すると、誘導放出が起こる(光増幅)。

入射光のエネルギーが、2 準位のエネルギー差に近いほど効率よく誘導放出が起こる。

図 II. 3.9 反転状態と誘導放出

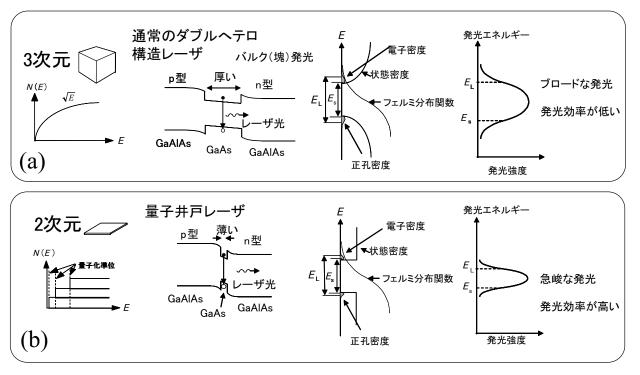

最初に半導体を用いて連続発振に成功したレーザの構造を図II.3.11(a)に示す。ダブルヘテロ構造と呼ばれ、バンドギャップが狭く光学的屈折率の大きなGaAsを、バンドギャップが広く屈折率の小さなGaAlAsでサンドイッチした構造である。ヘテロとは「異種の」という意味で、左右に2つの異種結晶の接合面があるのでこう呼ばれる。通常のp/n接合(III章参照)に電流を流すと、電子およびホールは、お互いに反対方向に流れるので、再結合確率が低く発光効率が低い。光も四方八方に広がっていくので、誘導放出の効率も悪い。これに対して、図(a)の構造では、電子とホールが中心のGaAs層に閉じ込められると同時に、電子・ホール再結合によって生じた光も、屈折率の大きなGaAs層に閉じ込められ(光ファイバと同じ原理)、誘導放出が効率良く起こる。この結晶を半波長の整数倍の長さにへき開(結晶面に沿ってきれいに割れる現象)して、その端面をミラーとして利用することにより、初めて室温で連続発振する半導体レーザが実現した。

初期の半導体レーザでは、GaAs 層が厚く、電子およびホールは3次元的に分布するため、状態密度は、図(a)に示すように放物線で表され、それらの持つエネルギーは比較的幅の広いものとなる。従って、発光波長もブロードとなり、誘導放出の効率は、次に述べる量子井戸レレーザに比べると劣る。

これに対して、GaAs 層を 2 次元系と見なせるほど薄くすると、図 (b) に示すように状態密度はステップ関数状になり、電子及びホールの占有するエネルギー幅が狭まる。このため、発光波長幅が狭まり、誘導放出の効率も上がり、効率の良いレーザができる。会議でよく使用されるレーザポインタには、この量子井戸レーザが用いられている。

## 低次元系のメリットの例(高効率量子井戸レーザ)

図 II.3.11 低次元系のメリットを生かしたデバイスの例(量子井戸レーザ)

## Ⅱ・4 半導体中の電子および正孔密度

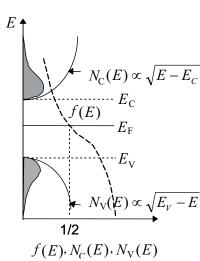

これまでに求めた分布関数および状態密度を用いて、半導体中の電子および正孔密度を求める。 (II・3・2) と (II・3・3) に、 (II・3・4) のフェルミ・ディラック分布関数と (II・3・10) の状態密度式を代入すれば電子および正孔の密度が求まる。ここで、状態密度の式は、図 II・4・1 中に示すように、電子および正孔について、それぞれ伝導帯の底  $E_c$  および価電子帯の頂上  $E_v$  を原点に書き換えている。 フェルミレベルが、 $E_c$  および  $E_v$  から kT に比べて十分離れているとして、フェルミ・ディラックの分布関数の分母の 1 を無視して計算すると、電子密度 n、および正孔密度 p は次式で与えられる。 (この節のエネルギー表記は全てジュール: I 単位。 I 単位ではないので要注意)

$$n = \int_{E_C}^{\infty} N(E) f(E) dE = N_C \exp\left(-(E_C - E_F)/kT\right)$$

(II.4.1)

ここに、

$$N_C = 2 \left( \frac{2\pi m_e kT}{h^2} \right)^{3/2}$$

伝導帯の有効状態密度、  $m_e$  は電子の有効質量 (II· 4· 2)

$$p = \int_{-\infty}^{E_V} N(E)(1 - f(E)) dE = N_V \exp(-(E_F - E_V)/kT)$$

(II· 4·3)

ここに、

$$N_{\nu}=2\left(\frac{2\pi m_{h}kT}{h^{2}}\right)^{3/2}$$

価電子帯の有効状態密度、  $m_{h}$ は正孔の有効質量(II· 4· 4)

ここで、pn 積を計算すると、

$$pn = N_C N_V \exp(-E_\sigma / kT)$$

(II· 4· 5)

$$E_{\sigma} = E_C - E_V \qquad ( \mbox{\it id} \mbox{\it id} \mbox{\it id} + \mbox{\it id} \mbox{\it id} ) \end{matrix} \end{matrix} ( \mbox{\it II} \cdot 4 \cdot 6 )$$

(II·4·5) より pn 積はフェルミレベルの位置に無関係で半導体のバンドギャップのみによって決まる。

#### ・真性半導体中の電子および正孔密度

真性半導体では、電子が価電子帯から伝導帯に熱励起されて、伝導電子および正孔が生成されるので、p=nであり、フェルミレベルはエネルギーギャップのほぼ中心にくる。この条件を (II·4·1) に代入すると、次式を得る。

$$p = n \equiv n_i = \sqrt{N_C N_V \exp(-E_g / kT)} \propto \exp\left[-E_g / (2 kT)\right]$$

(II· 4·7)

$n_i$ を真性キャリア密度と呼ぶ。 $n_i$ は温度を上げると増加し、エネルギーギャップ  $E_g$  の半分の活性化エネルギーをもつ。図 II. 4.2 に代表的な半導体の真性キャリア密度の温度依存性を示す。このように、

図 II. 4.1 真性半導体の伝導帯の 電子および価電子帯の正孔の密度

図 II.4.2 代表的半導体のキャリア密度の温度依存性 (アレニウスプロット)

横軸に 1/*T*、縦軸に物理量を対数でプロットしたものをアレニウスプロットと呼ぶ。アレニウスプロットにおける直線の傾きを活性化エネルギーと呼ぶ。アレニウスプロットは温度依存性を示す時に頻繁に使われる。

#### ・実際の半導体の伝導帯電子の等エネルギー面

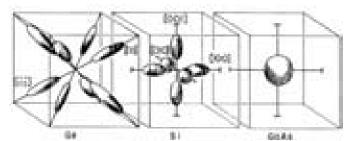

これまでは、電子の等エネルギー面は、運動量pまたは波数k空間において中心対称な球状と仮定してきた。実際の半導体ではどうなっているだろうか。図 II. 4.3 は、代表的な半導体 Ge, Si, GaAsの伝導帯電子のk空間における等エネルギー面の形状である。この形状は、サイクロトロン共鳴吸収の実験から決定される。GaAsでは球状なのでこれまでの扱いができ、1つの有効質量を用いて記述できる。しかし、Ge および Si では、等エネルギー面は回転楕円体であり、2つの有効質量を持つ。Si の場合エネルギーE は、図 II. 4.3 のk 軸の正方向に位置する回転楕円体に対して、次の式で表せる。

$$E(k_x, k_y, k_z) = \hbar^2 \left( \frac{k_x^2 + k_y^2}{2m_t} + \frac{(k_z - k_0)^2}{2m_l} \right)$$

(II· 4·8)

ここで、 $m_{\rm t}$ を横方向有効質量 (transverse effective mass)、 $m_{\rm t}$ を縦方向有効質量 (longitudinal effective mass) と呼び、 $m_{\rm t}$ =0.19 $m_{\rm 0}$ ,  $m_{\rm t}$ =0.916 $m_{\rm 0}$ ,  $m_{\rm 0}$  は電子の静止質量 =9.1x10 $^{-31}$ kg である。この場

図 II. 4.3 代表的半導体の伝導帯底付近の等エネルギー面の形状

表 II.1 室温 (300K) における代表的な半導体 Si, Ge, GaAs, GaN, SiC および絶縁体 SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>の基本的物性定数

|                                                |                                                 |                                                        |                                      |                      |                       | -                 |                              |                                |

|------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|--------------------------------------|----------------------|-----------------------|-------------------|------------------------------|--------------------------------|

|                                                |                                                 | Si                                                     | Ge                                   | GaAs                 | GaN                   | SiC(4H)           | SiO <sub>2</sub>             | Si <sub>3</sub> N <sub>4</sub> |

| バンドギヤップ                                        | $E_{\rm g}\left({\rm eV}\right)$                | 1.12                                                   | 0.68                                 | 1.42                 | 3.4                   | 3.26              | 8~ 9                         | ~5.3                           |

| 真性キャリア密度                                       | $n_{\rm i} ({\rm cm}^{-3})$                     | 1.5x10 <sup>10</sup>                                   | $2.5x10^{13}$                        | $1.1x10^{7}$         | 1x10 <sup>-8</sup>    | $1x10^{-8}$       |                              |                                |

| 抵抗率                                            | $\rho_{\rm R} (\Omega^{\rm c} {\rm cm})$        | $3.0x10^5$                                             | $6.4x10^{1}$                         | $7.0x10^{7}$         |                       |                   | ~1014                        | ~10 <sup>15</sup>              |

| 伝導電子の移動度                                       | $m_{\rm e} ({\rm cm}^2/{\rm V}^{\cdot}{\rm s})$ | 1500                                                   | 3900                                 | 8500                 | 900                   | 1000              |                              |                                |

| 正孔の移動度                                         | $m_{\rm h} ({\rm cm}^2/{\rm V}^{\cdot}{\rm s})$ | 600                                                    | 1900                                 | 400                  | 400                   | 120               |                              |                                |

| 電子の飽和速度                                        | (cm/s)                                          | $1.0x10^{7}$                                           | $6x10^6$                             | $2.0x10^{7}$         | $2.7x10^{7}$          | $2.7x10^{7}$      |                              |                                |

| 伝導電子の質量                                        | $m_{\rm e}$                                     | $m_t = 0.19 \text{m}_0$                                | $m_t = 0.082m_0$                     | $0.067m_0$           | 0.19m <sub>0</sub>    | $m_1 = 0.42 m_0$  |                              |                                |

| (m <sub>0</sub> =9.1x10 <sup>-31</sup> kg: 電子の | 静止質量)                                           | $m_1 = 0.98 m_0$                                       | $m_1 = 1.64 m_0$                     | 0.007m <sub>0</sub>  | 0.19m <sub>0</sub>    | $m_1=0.29m_0$     |                              |                                |

| 正孔の質量                                          | $m_{ m h}$                                      | $m_{\text{lh}} = 0.16m_0$<br>$m_{\text{hh}} = 0.49m_0$ | $m_{1h}=0.04m_0$<br>$m_{hh}=0.28m_0$ | $0.082m_0$           | 0.60m <sub>0</sub>    |                   |                              |                                |

| 比誘電率                                           | K                                               | 11.7                                                   | 16.0                                 | 12.0                 | 9.5                   | 10                | 3.9                          | 7.5                            |

| 耐圧                                             | $E_{\rm B}$ (V/cm)                              | $\sim 3 \times 10^5$                                   | ~10 <sup>5</sup>                     | $\sim 4x10^{5}$      | $3.3x10^{6}$          | $3.0x10^6$        | ~10 <sup>7</sup>             | ~10 <sup>7</sup>               |

| 原子密度                                           | $N \text{ (cm}^{-3})$                           | 5.0x10 <sup>22</sup>                                   | 4.42x10 <sup>22</sup>                |                      | 4.42x10 <sup>22</sup> |                   | 2.3x10 <sup>22</sup><br>(分子) |                                |

| 密度                                             | $\rho_{(g/cm^3)}$                               | 2.33                                                   | 5.33                                 | 5.32                 | 6.15                  | 3.21              | 2.27                         | 3.1                            |

| 伝導帯の実効状態密度                                     | $N_{\rm C}$ (cm <sup>-3</sup> )                 | 2.8x10 <sup>19</sup>                                   | 1.04x10 <sup>19</sup>                | 4.7x10 <sup>17</sup> |                       |                   |                              |                                |

| 価電子帯の実効状態密原                                    |                                                 | 1.02x10 <sup>19</sup>                                  | $6.1x10^{18}$                        | $7.0x10^{18}$        |                       |                   |                              |                                |

| 格子定数                                           | $a_0$ (Å)                                       | 5.43                                                   | 5.658                                | 5.654                | a=3.07<br>b=10.05     | a=3.07<br>b=10.05 |                              |                                |

| 融点                                             | (°C)                                            | 1420                                                   | 937                                  | 1238                 | > 2500                | 2730              | ~1600                        | ~1900                          |

| 熱伝導度                                           | $(W \cdot cm^{-1} \cdot {}^{\circ}C^{-1})$      | 1.45                                                   | 0.64                                 | 0.46                 | 2.1                   | 4.9               | 0.014                        | 0.3                            |

| 電子親和力                                          | χ (eV)                                          | 4.05                                                   | 4                                    | 4.07                 | 4.1                   | ~ 4.1             | 0.95                         | ~ 2.1                          |

合の状態密度を求める方法は、 $k_x$ ,  $k_y$  軸を  $(m_1)^{1/2}$  倍、 $k_z$  軸を  $(m_1)^{1/2}$  倍にした新たな k' 空間を導入する。 そこでは、等エネルギー面は球状になるので、これまでと同様な方法で状態密度が計算できる。このようにして求めた有効質量は  $(m_1m_1m_1)^{1/3}$  となる(状態密度質量と呼ぶ)。

表 II・1 に代表的な半導体および絶縁体の基本物性定数を示した。Si は高度な微細加工と集積技術が進歩しており、広く LSI 用半導体基板として用いられている。GaAs は直接遷移型半導体であり、発光デバイスとして利用されている。電子移動度が Si の約 6 倍と大きく、マイクロ波デバイスとして携帯電話などに使用されている。しかし、正孔の移動度が小さく、また Si のように CMOS 技術が確立されていないという欠点がある。Ge は電子移動度が Si の約 2 倍、正孔移動度は 3 倍と大きい。また、バンドギャップが小さいので赤外線用フォトディテクタとして用いられる。また Si との合金 Si Ge も高速なので、高速デバイスとして検討されている。

#### ・外因性半導体中の電子および正孔密度

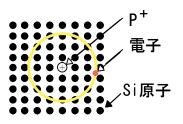

真性半導体である Si 結晶の原子の一部を V 族または III 族の原子で置換すると、伝導電子または 自由ホールが生成される。Si 中に P をドープした場合のモデルを図 II. 4.4 に示す。結合にあずから ない P の余分の電子は、イオン化した P\*イオンの周りを回る水素原子モデルで近似できる。水素原子との違いは、電子が回る空間が真空中ではなく、比誘電率  $\varepsilon_r$ =11.7 の Si 結晶である点と、電子の質量 が真空中の自由電子の質量ではなく、伝導帯中の有効質量になる点である。水素原子中の基底電子の 軌道半径であるボーア半径は 0.5 Å ( オングストローム  $=10^{-10}$  m) であるのに対して、Si 結晶中では誘電率が約 12 倍大きく、有効質量が 20% と小さいため軌道半径は約 3nm (1nm= $10^{-9}$  m) となる。イオン化エネルギーは、 $W_{DI}=mq^2/(8h^2\varepsilon_r^2\varepsilon_o^2)/n^2$ (ここに、 $\varepsilon_o$  は真空の誘電率、n は量子数)で与えられるので、水素原子が 13.6 eV に対して、Si 中のドナーでは 0.033 eV と見積もられる。この値は、表 II.2 に示した実測値 (0.039-0.04 eV) に近く、水素原子モデルが良い近似であることを示している。代表的な不純物である P と B による Si 中での不純物準位を図 II.4.5 に示す。

図 II.4.4 半導体中不純物の水 素原子模型

表 II.2 半導体 Si, Ga As 中の不純 物のイオン化エネルギー (測定値)

|      | 不純物 (タイプ) | エネルギー(eV) |

|------|-----------|-----------|

|      | P (n)     | 0.044     |

| Si   | As (n)    | 0.049     |

|      | Sb (n)    | 0.039     |

|      | B (p)     | 0.04 5    |

|      | Pt (n)    | 0.37      |

| GaAs | Te (n)    | 0.003     |

|      | Zn (p)    | 0.02 4    |

|      | Cr (p)    | 0.7       |

図 II.4.5 Si 中の P, B の不純物レベル

#### ・外因性半導体中のフェルミレベルとキャリア密度

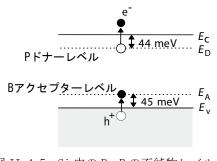

n型半導体およびp型半導体のバンドダイヤグラムを図II.4.6に示す。n型半導体では、V族不純物が作るドナーレベルが伝導帯底下数十meVに位置するため、室温の熱エネルギー(26meV)によって

図 II.4.6 n型および p 半導体のエネルギーバンドダイヤグラム

電子が伝導帯に熱的に励起され、電気伝導に寄与する伝導電子(キャリア)となる。p型半導体では、III 族不純物が作るアクセプターレベルが価電子帯頂上より数十meV 上に位置するため、熱エネルギーによって電子が価電子帯からアクセプターレベルに熱的に励起され、正孔(ホール)が形成されキャリアとなる。この時のフェルミレベルの位置、フェルミ・ディラック分布関数、伝導帯および価電子帯の状態密度、伝導帯電子密度nおよび価電子帯ホール密度pの様子も図中に示した。伝導帯電子密度nおよび価電子帯ホール密度pは、次式によって与えられる。

$$n = N_C \exp\left(-(E_C - E_F)/kT\right) \tag{II-4.9}$$

$$p = N_V \exp\left(-(E_F - E_V)/kT\right) \tag{II-4.10}$$

ここに、 $N_{\rm c}$ ,  $N_{\rm v}$  はそれぞれ、伝導帯および価電子帯の有効状態密とと呼ばれ、(II·4·2)、(II·4·4) に示した。これらは、 $E=E_{\rm c}$  および  $E=E_{\rm v}$ に  $N_{\rm c}$  個と  $N_{\rm v}$  個の状態が集中して存在しているのと同等であることを示している。

真性半導体の電子密度と正孔密度は等しく(=n<sub>i</sub>)次式で与えられる。

$$n_i = N_C \exp\left(-\frac{E_C - E_i}{kT}\right) = N_V \exp\left(-\frac{E_i - E_V}{kT}\right)$$

(II· 4· 11)

ここで、 $E_i$  は真性半導体のフェルミレベルである。上式を $E_i$  について解くと、

$$E_i = \frac{E_C + E_V}{2} - \frac{kT}{2} \ell n \left( \frac{N_C}{N_V} \right). \tag{II-4-12}$$

上式の第 2 項は 1 項に比べ小さい (室温の Si で 13meV:  $E_{\rm g}$  の 1.2%) ので、真性半導体のフェルミレベルは、バンドギャップのほぼ中央に位置する。

(II·4·9) および (II·4·10) の n, p を n<sub>i</sub> を使って表すと、

$$n = n_i \exp\left(\frac{E_F - E_i}{kT}\right), \quad p = n_i \exp\left(\frac{E_i - E_F}{kT}\right).$$

(II· 4· 13)

上式より、

$$pn = n_i^2$$

(II· 4· 14)

この式は、熱平衡条件下(熱以外の外乱、例えばバイアス電圧等が加わっていない状態)では、真性 半導体でも外因性半導体でも成立し、質量作用の法則と呼ばれる。

外因性半導体のフェルミレベルは、n型半導体では伝導帯底の近く、p型半導体では価電子帯頂上近くに位置する。その位置は、不純物濃度および温度によって変わる。今n型で考え、物理変数にnの添字をつける。イオン化ドナー濃度  $N_D$  を、イオン化アクセプター濃度を $N_A$  とする。

電荷中性条件と質量作用の法則より、  $n_n = p_n + N_D$ ,  $n_n p_n = n_i^2$  (II·4·15) この式を  $n_n$ ,  $p_n$  について解くと、

$$n_n = \frac{\sqrt{N_D^2 + 4n_i^2 + N_D}}{2}, \quad p_n = \frac{\sqrt{N_D^2 + 4n_i^2 - N_D}}{2}$$

(II· 4· 16)

通常  $N_D >> n_i$  なので  $n_n \approx N_D$ ,  $p_n = n_i^2/N_D$  (II·4·17)

p型半導体の場合は、

$$p_p \approx N_A$$

,  $n_p = n_i^2/N_A$  (II·4·18)

(II·4·9) と (II·4·13) または (II·4·17) の最初の式を両立させて解くと、n 型半導体中のフェルミレベルが求まる。

$$E_{F(n)} = E_i + kT \ell n \frac{N_D}{n_i} = E_C - kT \ell n \frac{N_C}{N_D}$$

(II· 4· 19)

同様にして、p型半導体中のフェルミレベルは次式で与えられる。

$$E_{F(p)} = E_i - kT\ell n \frac{N_A}{n_i} = E_V + kT\ell n \frac{N_V}{N_A}$$

(II· 4· 20)

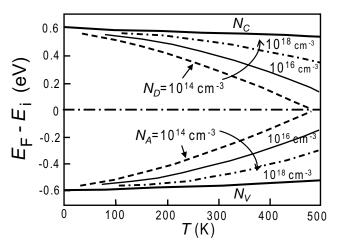

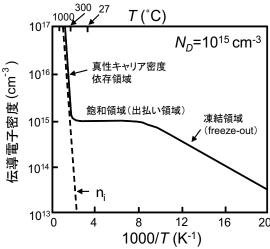

外因性半導体のフェルミレベルは、不純物濃度が高いほどバンド端に近づく。また温度が上がると真性半導体に近づくので、フェルミレベルはバンドギャップ中央に近づく。一方、温度が低くなると、不純物はイオン化できなくなり、フェルミレベルはバンド端に近づく。このような条件下では、(II・4・19)、(II・4・20) は適用できない(これらの式は不純物が全てイオン化した条件下で得られた)。フェルミレベルの不純物濃度依存性および温度依存性の例を図 II. 4. 7 に示す。また、n 型半導体の伝導帯の電子密度の温度依存性の例を図 II. 4. 8 に示す。

図 II.4.7 n型および p 半導体のフェルミレベル の不純物濃度および温度依存性

図 II. 4.8 n型半導体の電子密度の温度依存性

#### ・縮退半導体について

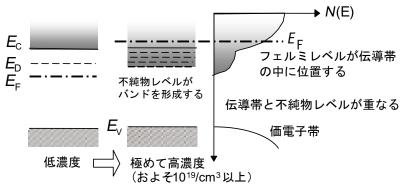

不純物濃度を大きくしていくと、不純物原子間の距離が短くなり、不純物レベル同士が相互作用する結果バンドが形成され伝導帯と繋がってしまう。この時、フェルミレベルは、伝導帯の中に位置し金属と類似の性質になる(図 II. 4.9)。このような半導体を縮退半導体と呼び、低温まで低抵抗なのでトランジスタのソース、ドレインなどの電極として用いられる。このような状態は不純物濃度がおよそ  $10^{19}/\mathrm{cm}^3$  以上で生じる。量子力学で使う「縮退」とは意味が異なる。

図 II. 4.9 縮退半導体のバンドダイヤグラムと状態密度

## Ⅱ・5 電子、正孔の輸送機構

物質中での電流には、キャリアが電界によって動くドリフト電流と、濃度勾配によって拡散する拡 散電流の2種類がある。

#### ・ドリフト電流

電子、正孔が、電界によって力を受け電流が流れる様子をミ クロに考察する。電子は熱運動しており、Si 結晶中の伝導電子 の速度は約 10<sup>7</sup>cm/s、即ち秒速 100km、1cm の距離を進む時間は  $0.1 \mu s$  である。熱速度は  $mv^2/2=3kT/2$  に、Si の伝導電子の有効 質量を代入して導かれる。統計力学によれば、1自由度に分配 される熱エネルギーは kT/2 であり、3 次元自由空間で運動して 図 II.5.1 電子の熱運動と電界印加時 いる電子はx, y, z方向の3自由度を持つので3kT/2となる。

無電界下の運動 (ランダム運動)

雷界下の運動

の運動

電子は、結晶格子の乱れ、不純物原子、結晶欠陥、他の電子や正孔などによってランダムな方向に 散乱(衝突)を繰り返している。その結果、電界のない時は正味(平均)の流れはない(図 II.5.1 左)。 電界を印加すると図 II.5.1 右に示すように、ランダムな熱運動に加えて電界方向の運動成分が加わ り1つの電子についての時間平均、または電子集団で平均すると正味の流れ(電流)が発生する。散 乱から次の散乱までの平均時間 τ を平均衝突時間(または緩和時間)、その間に走る距離 ℓ を平均自 由行程と呼ぶ。Si 結晶では、平均衝突時間は 10<sup>-13</sup>s、平均自由行程は 10nm 程度である。定常状態で は、電子は外部電界によって初速度=熱速度=ν,,から加速され、散乱によってそれまでに電界から得 たエネルギーを散乱中心(例えば格子)にもどし、再度熱速度でランダム方向に(等方的に)散乱さ れる、という行程が繰り返されていると考えられる。 散乱後、電界によって加速されて電界と逆方向(図 II.5.1 の左方向) に進む電子の数と、電界によって減速されて右側に進む電子数との差が正味の電流 となる。簡単のため電子密度nの1次元系を考える。散乱直後左に進む半数の電子n/2は、電界 $\varepsilon$ に よる力 F=-q  $\varepsilon$  によって時間  $\tau$ の間に  $\Delta v=(q \mathcal{E}/m_e) \tau$  だけ加速されるので、左方向の平均の流束  $N_+$  は、

$$N_{+}=(n/2)(v_{th}+(q\mathcal{E}/2m_{e})\tau). \tag{II} \cdot 5\cdot 1)$$

同様にして、散乱直後右に進む半数の電子は減速され、その平均の流束 N. は、

$$N_{-}=(n/2)(v_{th}-(q\mathcal{E}/2m_e)\tau). \tag{II} \cdot 5\cdot 2)$$

$差 N_+ - N_-$ が正味左に進む電子の流東 N になるので、

$$N=N_{+}-N_{-}=n(q\,\mathcal{E}/2m_{e})\,\tau. \tag{II} \cdot 5\cdot 3$$

従って、電子密度nの電子集団の平均速度v(ドリフト速度)はN=nvより、

$$v = (q \mathcal{E}/2m_e) \tau$$

. (II·5·4)

この式は、1 次元での近似式である。3 次元において、 $\Delta

u$  が  $u_{

m th}$  に比べ十分小さく、au = $m{e}/(

u_{

m th} + \Delta

u)$ 、 $m{\ell}$  -定の下に厳密に計算すると(付録 I.1. の三次元空間でのドリフト電流式の導出を参照)上式の分母 の係数 2 は 6 となる。一方、電子移動度 μ は次の式で定義される。

$$v = \mu_e \mathcal{E}$$

(II· 5· 5)

従って3次元での係数を代入した(II·5·4)と(II·5·5)から、

$$\mu_{\rm e} = q \, \tau / 6 m_{\rm e} \tag{II} \cdot 5 \cdot 6)$$

即ち、移動度  $\mu_e$  は、平均衝突時間  $\tau$  と有効質量  $m_e$  によって決まり、有効質量が小さいほど加速され やすく、平均衝突時間が長くなるほど最終速度は大きくなり、移動度は大きくなる。正孔の場合も (II·5·6) と同様の式が成立する。(II·5·4)、(II·5·6) の分母の係数は1とした教科書が多いが、納 得できる説明をしたものはほとんどない。

平均衝突時間は散乱中心の密度や電子、正孔の速度によって決まる。

散乱中心には次の3種類がある。

- (1) 格子散乱 (結晶格子の不完全性による散乱)

- (2) 不純物散乱 (イオン化不純物散乱と中性不純物散乱の2種だが後者は通常極めて小)

- (3) キャリア間散乱

エネルギー的観点からは、次の2種類の散乱がある。

- (1) 弾性散乱(電子のエネルギーは変わらない)

- (2) 非弾性散乱(電子のエネルギーが一部失われる)

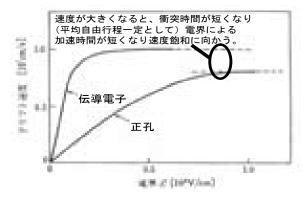

図 II. 5.2 に Si 中の電子と正孔のドリフト速度の電界強度依存性を示す。弱電界下では、 $\Delta \nu < \langle \nu_{\rm th} \rangle$  のため  $\tau$  は一定、 $\mu_{\rm e}$  も一定でドリフト速度  $\nu$  は電界強度に比例する。電界強度が大きくなると  $\tau$  は短くなり速度は飽和に向かう。平均自由行程に比べ大きなデバイスでは、結晶格子による非弾性散乱の結果速度飽和が起こるが、微細デバイスでは、無衝突のため飽和速度以上のドリフト速度、いわゆる「速度オーバーシュート」が報告されている。

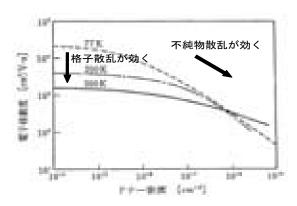

図 II.5.3、図 II.5.4 に、Si 及び GaAs の電子及び正孔移動度の不純物濃度依存性を示す。不純物濃度が増大すると、不純物散乱により移動度が減少することがわかる。不純物は結晶中にランダムに配置され、結晶の周期場を乱しているため、散乱中心として作用する。図 II.5.3 から、低温にすると格子の熱振動が減少するため格子散乱が減少し、移動度が向上することが分かる。

図 II.5.2 ドリフト速度の電界強度の関係(Si)

図 II.5.3 電子移動度とドナー濃度の関係 (Si)

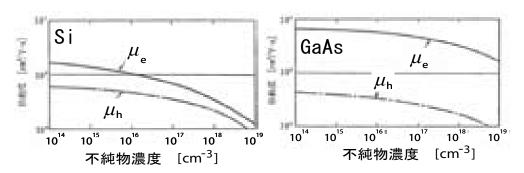

図 II.5.4 Si および GaAs の電子、正孔移動度の不純物濃度依存性

図 II.5.5 Si における抵抗率と不純物濃度の関係

#### ・半導体の抵抗率

半導体の電気抵抗率ρは電気伝導度(導電率)σの逆数であり、次式で表される。

$$\rho = 1/\sigma = 1/(qn\mu_e + qp\mu_h) \tag{II-5.7}$$

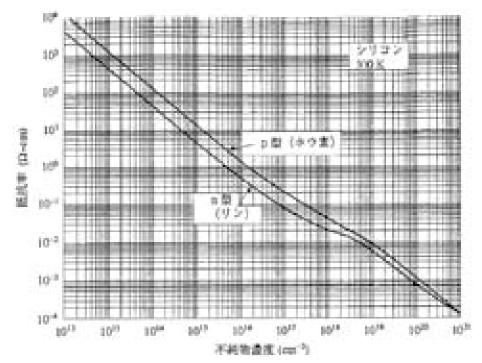

電気抵抗率 $\rho$ は、単位体積の物質の電気抵抗で定義される。実測した n 型および p 型 Si 結晶の抵抗率と不純物濃度の関係を図 II.5.5 に示す。室温では、浅いドナーやアクセプターはすべてイオン化していて、不純物濃度が  $10^{17}$  cm<sup>-3</sup> より低い場合には抵抗率は不純物濃度に比例する。高濃度領域では、不純物散乱や縮退効果等によって、非線形性が観測される。

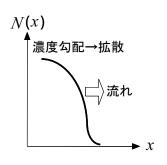

#### • 拡散流

電界が無くても、キャリア密度勾配が存在すると濃度の高い所から低いところに拡散流 F が生じる (図 II. 5. 6)。 定量的には次式で与えられる。

$$F_e = -D_e \frac{dn}{dx}$$

電子

$$F_h = -D_h \frac{dp}{dx}$$

正孔 (II· 5· 8)

ここに、Fは流れ密度、Dは拡散係数である。添え字はキャリアの種類で、e は電子、h はホールを示す。

#### ・電流密度の式

電流は、電界によるドリフト電流と濃度勾配による拡散電流の和として次式で与えられる。

図 II.5.6 濃度勾配による拡散

電子による電流

$$J_e = qn\mu_e \mathcal{E} + qD_e \frac{dn}{dx}$$

(II·5·9)

正孔による電流

$$J_h = qn\mu_h \mathcal{E} - qD_h \frac{dp}{dx}$$

(II·5·10)

2項目の拡散電流の符号が、電子と正孔で異なっているのは、それ ぞれの電荷が逆符号のためである。

ここまでに登場してきた各種定数の間には、次のアインシュタイン の関係式が成立している。

$$\frac{D_e}{\mu_e} = \frac{kT}{q}, \qquad \frac{D_h}{\mu_h} = \frac{kT}{q}$$

(II· 5· 11)

#### キャリア連続の式

キャリアの流れF(単位:例えば、個/cm²-s)に分布がある場合を考える(図 II. 5. 7)。微小体積dx内に流れ込む正味の流れは、次式で与えられる。

$$F(x) - F(x + dx) = F(x) - \left\{ F(x) + \frac{\partial F(x)}{\partial x} \cdot dx \right\}$$

$$= -\frac{\partial F(x)}{\partial x} \cdot dx$$

(II. 5. 12)

単位体積当たりに、単位時間に流れ込む正味の流れ(単位:例えば、個/ $cm^3$ -s)は、上式を dx で除して

$$-\frac{\partial F(x)}{\partial x} \tag{II-5.13}$$

したがって、流れと発生・再結合が共存する時は、次式が成立する。

$$\frac{\partial n}{\partial t} = G_L - U - \frac{\partial F_e}{\partial x}, \qquad \frac{\partial p}{\partial t} = G_L - U - \frac{\partial F_h}{\partial x}$$

(II· 5· 14)

ここに、n は電子密度、p は正孔密度、 $F_e$  は電子の流れ、 $F_h$  は正孔の流れ、 $G_L$  は電子・正孔対の発生レート(例えば光励起による生成)、U は再結合速度である。

流れの源は、電界によるドリフトと拡散の故、

電子に対して、

$$F_e = -n\mu_e \mathcal{E} - D_e \frac{dn}{dx} = -\frac{1}{q} J_n$$

(II·5·15)

正孔に対して、

$$F_h = p\mu_h \mathcal{E} - D_h \frac{dp}{dx} = \frac{1}{q} J_p$$

(II· 5· 16)

(II·5·15) と (II·5·16) を (II·5·14) に代入すると、次式を得る。

$$\frac{\partial n}{\partial t} = \frac{1}{q} \frac{\partial J_n}{\partial x} + G_L - U, \qquad \frac{\partial p}{\partial t} = -\frac{1}{q} \frac{\partial J_p}{\partial x} + G_L - U$$

(II· 5· 17)

この式を、キャリア連続の式と呼ぶ。物理的意味は、質量保存の法則である。単位体積当たりのキャリア密度の時間変化は、流れ込み(負の発散)と、発生、再結合(符号は負)の和に等しいという、ごく当たり前のことであるが、半導体中のキャリアの挙動を記述する重要な式のひとつである。

#### ・ポアソン方程式

半導体中の静電場を求めるための基本式は、次のポアソン方程式である。

$$\nabla^2 \phi = -\frac{\rho}{\varepsilon}, \qquad \overrightarrow{\mathcal{E}} = -grad \ \phi \tag{II.5.18}$$

ここで、 $\phi$  は静電ポテンシャル(電位)、 $\rho$  は電荷密度、 $\epsilon$  は媒質の誘電率、 $\vec{\mathcal{E}}$  は電界である。  $\rho$  は次式で与えられる。

$$\rho = q(p + N_D - n - N_A) \tag{II-5.19}$$

ここに、 $N_D$ はイオン化ドナー密度(正電荷)、 $N_A$ はイオン化アクセプター密度(負電荷)である。

#### ・擬フェルミ準位 (Imref) (逆に読むと Fermi))

半導体中のキャリア密度分布を求めるために、擬フェルミ準位と呼ばれるエネルギーレベルを導入 すると、数式が著しく簡素化され見通しの良いものとなる。

(i) 熱平衡状態 (印加電圧 0V で、電流が流れていない、時間∞で熱平衡に達した状態)での、キャリアの分布を表す式は (II・4・13) に示されている。擬フェルミ準位とは、非熱平衡化 (熱以外に、外部から電圧を印加し、電流が流れている熱平衡でない状態)でも、この式と類似の式が成立するとしたときのフェルミレベルに相当するエネルギーレベルのことである。以下、数式を用いて説明する。熱平衡化、電圧を印加しない状態でのフェルミレベルを用いたキャリア密度の式は、以下の通り。

$$n = n_i \exp\left(\frac{E_F - E_i}{kT}\right) \equiv n_i \exp\frac{q(\Psi - \phi)}{kT}$$

(II· 5· 20)

$$p = n_i \exp\left(\frac{E_i - E_F}{kT}\right) \equiv n_i \exp\left(\frac{q(\phi - \Psi)}{kT}\right)$$

(II· 5· 21)

ここに、

$$\Psi \equiv -\frac{E_i}{q}, \qquad \phi \equiv -\frac{E_F}{q}$$

(II· 5· 22)

この時、  $pn = n_i^2$  (II· 5· 23)

(ii) 次に、非熱平衡下、熱以外に外部から電圧を印加して電流が流れている状態において、次の式を満足する、 $\phi_n$  と  $\phi_p$  を定義する。

$$n \equiv n_i \exp \frac{q(\Psi - \phi_n)}{kT} \tag{II-5.24}$$

$$p \equiv n_i \exp \frac{q(\phi_p - \Psi)}{kT}$$

(II· 5· 25)

この ø と ø をそれぞれ、電子及び正孔に対する擬フェルミ準位と呼ぶ。

このとき、熱平衡ではないので、 $pn \neq n_i^2$  (II·5·26)

擬フェルミ準位を導入すると、電流は次のように表せる。

電流の式は、

$$\overrightarrow{J}_{n} = q\mu_{e}n \overrightarrow{\mathcal{E}} + qD_{e}\nabla n = q\mu_{e}\left(n\overrightarrow{\mathcal{E}} + \frac{kT}{q}\nabla n\right)$$

(II. 5. 27)

$$\overrightarrow{\mathcal{E}} = -\nabla \Psi \tag{II. 5. 28}$$

であることを用いると、

図 II.5.8 pn 接合のバンドダイヤグラム (a) ゼロバイアス、(b) 逆バイアス電圧印加時の擬フェルミ準位

$$\vec{J}_{n} = q\mu_{e} \left( n\vec{\mathcal{E}} + \frac{kT}{q} \nabla n \right) = q\mu_{e} n \left( -\nabla \Psi \right) + q\mu_{e} \frac{kT}{q} \left[ \frac{qn}{kT} \left( \nabla \Psi - \nabla \phi_{n} \right) \right]

= -q\mu_{e} n \nabla \phi_{n}$$

(II. 5. 29)

と非常に簡略化して表すことができる。正孔に対しても同様にして、

$$\vec{J}_p = q\mu_p p \nabla \phi_p \tag{II-5.30}$$

即ち、擬フェルミ準位を用いると、電流はドリフト電流と拡散電流を含めて、擬フェルミ準位の gradient が有効電界に等しいとしたドリフト電流のみで表すことができる。

図 II. 5.8 に、pn 接合に逆バイアス電圧を印加した時の擬フェルミ準位の例を示した。

## II・6 半導体内の電界・電流分布の計算法

半導体デバイス内での電界、電流分布を求める方法には、次の2種類がある。

- (1) 流体モデル (多数個のキャリアの動きを平均化して連続流体とみなして取り扱うモデル)

- (2) モンテカルロ法(キャリアを流体ではなく、個々の粒子として取り扱う方法) ここでは、(1)の流体モデルについて述べる。

次の3つの方程式を連立させ、境界条件を与えて解く(特殊な簡単な場合を除き、コンピュータによ る数値解法を用いる)

(1) ポアソン方程式(電界分布と電荷分布の関係を与える)

$$\nabla^2 \phi = -\frac{q}{\varepsilon} \left( p + N_D - n - N_A \right) \tag{II-6.1}$$

(2) 電流連続式(電流分布と電荷密度時間変化の関係を与える、定常状態では時間微分項=0)

$$\frac{\partial n}{\partial t} = \frac{1}{q} \frac{\partial J_n}{\partial x} + G_L - U, \qquad \frac{\partial p}{\partial t} = -\frac{1}{q} \frac{\partial J_p}{\partial x} + G_L - U$$

(II· 6· 2)

(3) 電流密度式(電流分布と電荷分布、擬フェルミ準位、バンドの曲がりとの関係を与える)

$$\vec{J}_n = -q\mu_e n \nabla \phi_n, \qquad \vec{J}_p = q\mu_h p \nabla \phi_p \tag{II-6.3}$$

#### 問題 II.

- (1) x, y, z の 3 方向に閉じ込められた電子(0次元電子)の状態密度は、 $N(E)=16\delta(E-E_{ijk})$ となるこ とを説明せよ。ここに、 $\delta(x)$  はx=0 で $\infty$ で、積分値が 1 となるデルタ関数、 $E_{i,j,k}$  は量子化エネルギー である。

- (2) 伝導帯における電子の等エネルギー面が (II·4·8) で表される時、状態密度質量が  $(m,m,m,m)^{1/3}$  と なることを導け。

- (3) 3次元空間においては、(II·5·6)の分母の係数が2でなく6になることを導け。

- (4) ノンドープ Si の伝導度を 300℃付近で測定した。伝導度の活性化エネルギーは何 eV か?

## ●コラム1

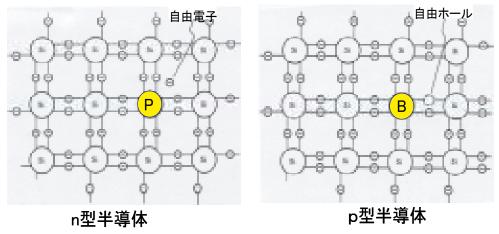

## n型、p型半導体の説明図

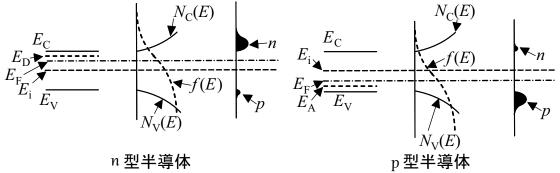

教科書やインターネットで、n型、p型半導体のキャリアである、自由電子、自由ホールの説明図として、下のような図をよく見かける。

図コラム 1.1 誤った半導体キャリアの説明図

どこが間違っているかおわかりだろうか。図の自由電子は決して自由ではない。P原子に束縛されている。同様に右図に自由ホールとあるが、これも間違いでB原子に束縛されている。正しい図は、本文の図II.1.5 の通りである。すなわち、P原子の最外殻電子のうち結合にあずからない余剰電子が、熱エネルギーでP原子の束縛から解かれたものが自由電子である。同様に、B原子の最外殻電子の数が共有結合に足りない分を、他のSi原子から熱エネルギーの力を借りて奪ってきた結果、できたSi格子の中の電子の空ポストが自由ホールである。このことは、本文の図II.2.6 を見れば明らかである。しかし、巷にある図は、ほとんどが上図のように間違っている。嘆かわしいことである。一度誰かが間違った図を描くと、教科書を書く先生ですら、深く考えずにコピペする結果であろう。かくいう私も第9版の教科書の前は、間違いに気づいていなかったのである。

## III. MOS トランジスタの物理

MOSトランジスタの電気特性を決める主要部分は、図 I.2.1 に示す、p-n 接合(ソース、ドレインと基板間の接合)および MOS (Metal-Oxide-Semiconductor) 構造 (ゲートー基板間の構造) である。この章ではこれらの電気特性について学ぶ。

## III・1 p-n 接合

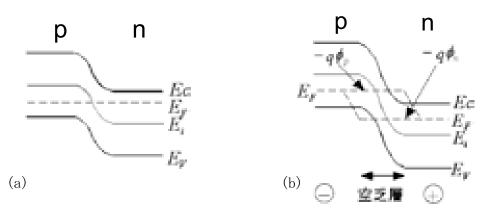

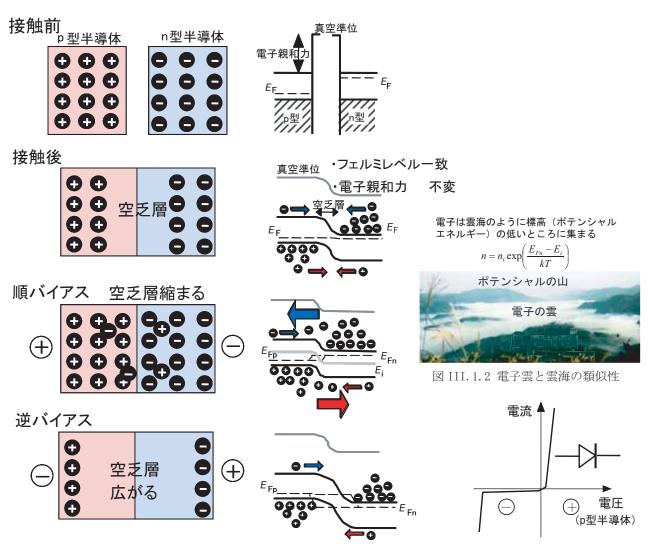

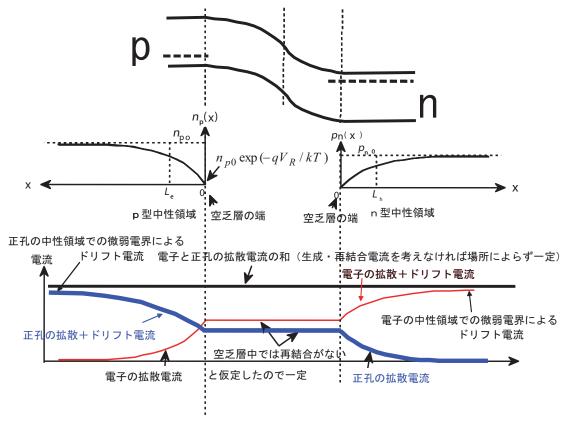

p-n 接合  $(p-n \ junction)$  における、電子、正孔の実空間およびエネルギーバンドダイヤグラム上での分布を図  $III.\,1.\,1$  に示す。

- (1) p型、n型半導体を接触する前の状態では、両者の真空準位が一致している。

- (2) p型とn型半導体を接触させる。電子はII 章で学んだようにフェルミ分布に従って分布する。 図 III.1.2 に示すように、ポテンシャルエネルギーの低いところが高密度になる。接触直後は 同じエネルギーにおいて、p型とn型半導体で正孔および電子密度が異なるため、接合界面に

図 III.1.1 p-n 接合中のキャリア分布と電流

図 III.1.3 p-n 接合の電流 - 電圧特性

おいてn型半導体の電子はp型半導体に移動し、p型半導体の正孔はn型半導体に移動する。フェルミレベルが一致し、p型、n型共にどの部分においても、電子及び正孔が同じ分布関数に従うようになると移動は止まる。熱平衡とは、場所によらず粒子が同じ分布関数に従う状態のことである。熱平衡状態では、どの断面をとっても左右へのキャリアの流れは等しく、正味の電流はゼロである。接合界面には、p側の空乏層中には、正孔が移動したことによって取り残された、負にイオン化したアクセプターイオンが存在し、n側の空乏層中には、電子が移動したことによって取り残された、正にイオン化したドナーイオンが存在する。その結果、p側は負に、n側は正に帯電し、電位差が生じている(内蔵電位または拡散電位と呼ぶ)。

- (3) 順バイアス電圧(たくさん電流が流れる向きの電圧、p側に+、n側に-の向き)を印加すると、分布関数にアンバランスが生じる。n側に負バイアスを印加すると、電子のポテンシャルエネルギーを増加させる(ポテンシャルエネルギー=-qVに注意、Vは印加電位)ので、n側のフェルミレベルはp側のそれに比べ高エネルギー側(上方向)にシフトする。その結果、n側の、エネルギー障壁(高さ=拡散電位-印加電圧)を超えてp側に移動可能な電子密度は、p側の電子密度より大きくなる。電子は熱速度で等方的に運動しているが、密度差があるため、nからp側へ正味の電子拡散流が発生する。同様に、pからn側へ正味の正孔拡散流が発生する。その結果、順バイアス電圧の増加と共に大きな電流が流れる。順バイアス電圧印加によって、p、n半導体間の電位差は減少し空乏層幅は減少する。

- (4) 逆バイアス電圧(電流が流れにくい向きの電圧、p 側に-、n 側に+)を印加すると、n 側のフェルミレベルはp 側のそれに比べ下方向にシフトする。したがって、エネルギー障壁(高さ=拡散電位 + 印加電圧)を超えてn 側からp 側に移動可能な電子密度は、p 側の電子密度よりきわめて小さくなる。しかし、p 側の電子密度は元々小さいため( $n=n_i^2/N_A$ )、電子密度差によって生じる拡散電流はわずかである。逆バイアス電圧印加によって、p、n 半導体間の電位差は増大し空乏層は広がる。破壊電界強度以上の電圧が印加されると、降伏現象により電流は急激に増加する。

以上説明した p-n 接合における電流一電圧特性の模式図を図 III. 1.3 に示す。

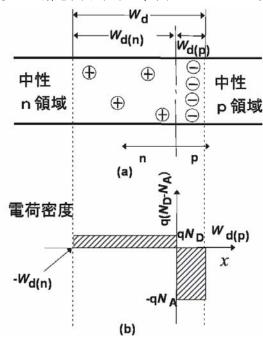

次に、空乏層幅および内蔵電位を計算する。基本方程式は次のポアソン方程式である。

$$\frac{d^2\phi}{dx^2} = \begin{cases}

-\frac{qN_D}{K\varepsilon_0} & (-W_{d(n)} \le x \le 0) \\

\frac{qN_A}{K\varepsilon_0} & (0 \le x \le W_{d(p)})

\end{cases}$$

(III-1-1)

ここに、Kは Si の比誘電率、 $N_D$ 、 $N_A$ はそれぞれ、イオン化ドナーおよびアクセプター密度である。この式を、次の境界条件の下で解く。

$$x = -W_{d(n)} \quad \text{old} \quad \frac{d\phi}{dx} = 0$$

$$x = W_{d(p)} \quad \text{old} \quad \frac{d\phi}{dx} = 0, \quad \phi = 0$$

(III-1-2)

その解は、次の式で与えられる。

なうれる。

$$\phi = -\mathcal{E}_{\text{max}} \left( x + \frac{x^2}{2W_{d(n)}} - \frac{W_{d(n)}}{2} \right) = -\frac{\mathcal{E}_{\text{max}}}{2W_{d(n)}} \left( x + W_{d(n)} \right)^2 + \mathcal{E}_{\text{max}} W_{d(n)} \\ \phi = \frac{W_{d(p)}}{2} \mathcal{E}_{\text{max}} \left( 1 - \frac{x}{W_{d(p)}} \right)^2$$

(111·1·3)

$$\mathcal{E}_{\max} = \frac{qN_D}{K\varepsilon_0} W_{d(n)} = \frac{qN_A}{K\varepsilon_0} W_{d(p)} \tag{III-1-4}$$

$\mathcal{E}_{\max}$ は、位置 x=0 における電界強度であり、この位置で最大値を取る。以上の解を図示すると、図 III. 1.4 のようになる。

図 III. 1.4 p-n 接合における電荷密度、電界および電位分布図

また、 $W_{d(n)}$ ,  $W_{d(p)}$ は次式で与えられる。

$$W_{d(n)} = \sqrt{\frac{2K\varepsilon_0 N_A \phi_{bi}}{q N_D (N_A + N_D)}} , \quad W_{d(p)} = \sqrt{\frac{2K\varepsilon_0 N_D \phi_{bi}}{q N_A (N_A + N_D)}}$$

(III· 1· 5)

ここに、 $\phi_{bi}$ は、p型とn型半導体間の電位差で、内蔵電位または拡散電位と呼ばれ次式で表される。

$$\phi_{bi} = \frac{kT}{q} \ell n \frac{N_A N_D}{n_i^2} \tag{III} \cdot 1 \cdot 6)$$

空乏層幅は、(III·1·5) の 2 項の和で、

$$W_d = W_{d(n)} + W_{d(p)}. \tag{III-1.7}$$

$N_D$  $<< N_A$  の場合(片側階段接合)は、

$$W_{d(n)} = \sqrt{\frac{2K\varepsilon_0\phi_{bi}}{qN_D}}$$

,  $W_{d(p)} \to 0$  (III·1·8)

即ち、空乏層は不純物密度の低い方に伸びる。この様子を図 III. 1.5 に示した。

外部電圧Vを印加した場合(p側に対してn側に+Vの電圧)には、 $\phi_{bi} \rightarrow \phi_{bi}$ +Vと置き換えれば良い。即ち、

$$W_{d(n)} = \sqrt{\frac{2K\varepsilon_0(\phi_{bi} + V)}{qN_D}} . \qquad (III \cdot 1 \cdot 9)$$

逆方向バイアス電圧を印加 (V>0) すると、空乏層は拡がり、順方向電圧印加 (V<0) で空乏層は縮まる。

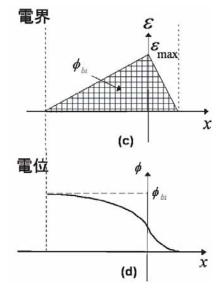

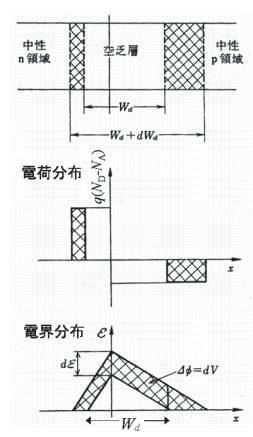

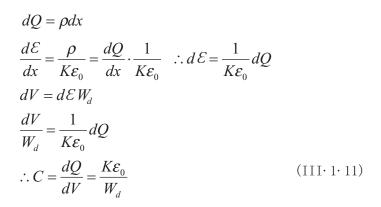

次に、p-n 接合の容量一電圧特性について考える。微分容量 C は次式で定義される。

$$C = \frac{dQ}{dV} \tag{III-10}$$

逆方向バイアス電圧を dV(>0) だけ増加させた場合の電荷 分布と電界分布の変化の様子を図 III.1.6 に示す。図より、Cは (III·1·11) のように求まる。

$N_A >> N_D$  の場合

$N_{\rm A} << N_{\rm D}$  の場合

図 III.1.5 片側階段接合の空乏層幅

図 III.1.6 逆方向バイアス電圧をわずか に増加した場合の電荷、電界分布の変化

図 III. 1.7 C-V 特性から不純物濃度、内蔵電位を求める方法

すなわち、微分容量Cは空乏層を絶縁層とした平行平板コンデンサの静電容量の式と同じ形で表せる。

$N_D << N_A$  の片側階段接合の場合は、(III·1·9) を用いて、

$$C = \sqrt{\frac{qK\varepsilon_0}{2} \cdot \frac{N_D}{\phi_{bi} + V}}$$

$$\psi \gtrsim iC, \quad \frac{1}{C^2} = \frac{2}{qK\varepsilon_0 N_D} \cdot (\phi_{bi} + V) \quad . \tag{III-1-12}$$

(III・1・12) を図示すると、図 III. 1.7 となる。容量の二乗の 逆数を縦軸に、逆方向電圧を横軸に取ってプロットすると、 逆方向電圧領域では直線に載り(順方向では大きな電流が流 れるため容量測定は困難になる)、その傾きから不純物濃度  $N_{\rm D}$  が、また横軸切片から内蔵電位  $\phi_{\rm bi}$  が求まる。

#### ・p-n 接合の形成方法

大きく分けて次の3種類がある。

- (1) 拡散法

- (2) イオン注入法

- (3) 合金法

# n 型シリコン p 型シリコン

図 III. 1.8 拡散法による p-n 接合の形成

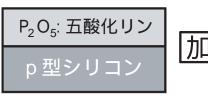

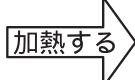

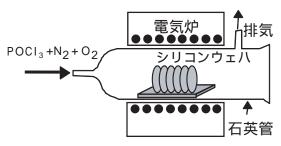

(1) 拡散法は、熱によって不純物を拡散する方法である。不純物として P を拡散する場合の概要、装置図および作業の様子を図 I I I . 1.8 に示す。P0C1 $_3$ (オキシ 3 塩化燐)という液体を窒素ガスでバブリングして、酸素ガスといっしょに電気炉に流す。Si 表面には 5 酸化燐の膜が形成され、そこから Si に P が拡散する。

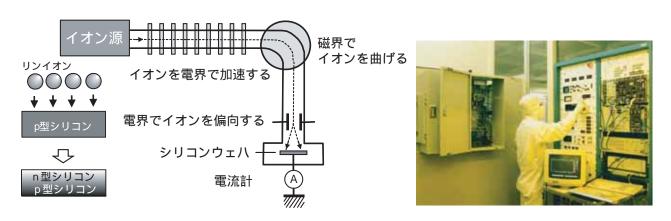

図 III. 1.9 イオン注入法による p-n 接合の形成およびイオン注入装置写真

(2) イオン注入法は、高速に加速されたイオンを Si 表面から物理的に叩き込む方式であり、熱拡散 に比べ低い温度で深い接合が容易に形成できる。またドーズ量を電気的にモニタ・制御できるので広 く用いられている。イオン注入装置の概略を図 III. 1.9 に示す。

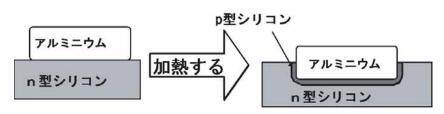

図 III. 1.10 合金法による p-n 接合の形成

(3) 合金法の概略を図 III.1.10 に示す。固体拡散源との合金反応を利用して不純物を拡散させる方法であるが、最近はあまり使用されない。

#### ・p-n 接合の電流一電圧特性

p-n 接合の理想電流電圧特性は、次の式で与えられる。

(1) 逆方向バイアス印加時

$$I_R = q \left( \frac{n_i W_d}{\tau_o} + \frac{D_e}{L_e} n_{p0} + \frac{D_h}{L_h} p_{n0} \right)$$

(III· 1· 13)

ここに、 $\tau_g$  は空乏層中でのキャリアの生成時定数、 $L_e \equiv \sqrt{D_e \tau_e}$ ,  $L_h \equiv \sqrt{D_h \tau_h}$  はそれぞれ電子および正孔の拡散長、 $\tau_e$  と  $\tau_h$  は電子及び正孔の再結合寿命、 $n_{p0}$ ,  $p_{n0}$  は p 型及び n 型半導体中の電子及び正孔の平衡時の密度である。第 1 項は空乏層中でのキャリアの熱生成による電流、第 2 項と第 3 項は、それぞれ p 型及び n 型半導体中の少数キャリアである電子及び正孔による拡散電流である。理想的には、電圧に依存しない。エネルギーギャップの小さい半導体ほど、 $n_i$  が大きく  $\tau_g$  が短くなるので空乏層中でのキャリア生成による電流が増加する。

#### (2) 順方向バイアス印加時

$$I_F = q \left( \frac{n_i W_d}{\tau_g} \exp \left( \frac{q V_F}{2kT} \right) + \left( \frac{D_e}{L_e} n_{p0} + \frac{D_h}{L_h} p_{n0} \right) \left[ \exp \left( \frac{q V_F}{kT} \right) - 1 \right] \right)$$

(III· 1· 14)

ここに V<sub>F</sub> は順方向の印加電圧である。

第1項は空乏層中でのキャリアの再結合電流、第2項がp型及びn型半導体中の少数キャリアによる拡散電流である。

順方向電流を、

$$I_F \propto \exp\left(\frac{qV_F}{nkT}\right) \tag{III·1·15}$$

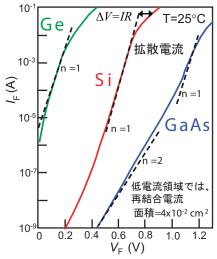

図 III. 1.11 p-n 接合の順方向 I-V 特性の例

という形に表したとき、n を理想係数と呼ぶ。空乏層中でのキャリアの再結合電流が主の場合には、n=2 となり、拡散電流が支配的な場合には、n=1 となる。

図 III. 1. 11 に実際の p-n 接合の順方向電流電圧特性の例を示す。低電流域では、捕獲準位密度によって支配される再結合電流が主 (n=2) であるが、大電流域では拡散電流が支配的 (n=1) になる。さらに大電流では、直列抵抗 R のため I-V 特性は  $\Delta V=IR$  だけシフトし、より寝てくる。

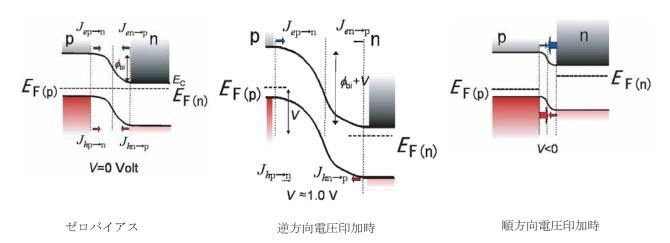

p-n接合の電流電圧特性の導出はここでは行わないが、整流性がえられるイメージ図を図 III.1.12 に再掲する。

#### (1) ゼロバイアス時

電子及び正孔共に左右方向の電流はつりあっていて正 味の電流はゼロである。電子について見ると、p側からn

側への電子の流れ  $J_{\text{ep}\to n}$  と、逆向きの流れ  $J_{\text{en}\to p}$  が存在する。 エネルギー的観点から、 p 側の伝導帯 の電子は全て、  $J_{\text{ep}\to n}$  に寄与できる。一方、 n 側の伝導帯の電子のうち、エネルギー  $E_c$  から  $E_c$  +  $\phi_{\text{bi}}$  の範囲の電子は、ポテンシャルエネルギーが低く、p-n 接合界面の電位障壁(高さ  $\phi_{\text{bi}}$ )を越えられないので、  $J_{\text{en}\to p}$  に寄与できない。ゼロバイアス時は、 $J_{\text{ep}\to p}$ = $J_{\text{en}\to p}$  である。

#### (2) 逆方向バイアス時

図のように p-n 接合界面の電位障壁が大きくなり(高さ  $\phi_{\rm bi}$ +V)、 n 側から p 側への電子の流れ  $J_{\rm en \to p}$  が著しく減少し無視できるようになり、 $J_{\rm ep \to n}$  がリーク電子電流となる。リーク電流は  $J_{\rm ep \to n}$  と  $J_{\rm hn \to p}$  の和で与えられ、それぞれ拡散によって決まり第 2,3 項となる。逆バイアスの場合、空乏層が 広がりその中の電界強度が大きくなるので、空乏層中で熱的に発生するキャリアが電流に効いてくる。

図 III. 1.12 p-n 接合に流れる電流

熱平衡状態(ゼロバイアスの場合)では、熱的に発生した電子・正孔対は、再び再結合してしまうので電流には寄与しないが、電界が大きいと、発生したキャリアは電界によって速やかに移動するため、再結合せず電流となる。これによる電流が(III·1·13)の第1項である。

図 III. 1.13 逆方向バイアス印加時の各電流成分の空間分布

#### (3) 順方向電圧印加時

空乏層端の少数キャリア密度は  $\exp\left(qV_F/kT\right)$  に増加するので、拡散電流は (III· 1· 14) 第 2 項のように電圧の指数関数で増大する。一方、順方向バイアス下では、空乏層中のキャリア密度の積が  $n_i^2$  を越えるため、再結合電流が発生し (III· 1· 14) 第 1 項で与えられる。

図 III. 1.13 には、逆方向バイアス印加時の各電流成分の空間分布の例を示す。

### ・トンネルダイオード (エサキダイオード)

p-n 接合において、p,n 半導体共に不純物濃度を大きくしていき、どちらも縮退半導体にしたものがトンネルダイオード、別名エサキダイオードであり、負性抵抗が観測される。江崎氏は、この業績によって 1973 年にノーベル物理学賞を受賞した。図 III. 1. 14 にその動作原理を示す。p,n どちらも縮退半導体であるため、図のように、フェルミレベルは、それぞれ価電子帯および伝導帯の中に入っている。不純物濃度が極めて高いため、空乏層幅は極めて短くなり電子がトンネルできるほどになっている (~10nm)。電子のトンネルは同じエネルギーレベル間で起こり、始状態の電子密度と終状態の空き準位密度に比例する。ゼロバイアスから順方向側に電圧を増加させていくと、伝導帯の電子は価電子帯の空き準位にトンネルし、伝導帯電子の占めるエネルギー幅と空き準位の重なりが増すので、トンネル電流は増加していく(p-1 または p-1 または p-1 を分と、終状態のエネルギーがバンドギャップ中に位置するようになり、終状態空き準位密度が減少するため、トンネル電流は減少する (p-1 なり、さらに電圧を増加させると、空乏層の電位障壁を越えるリーク電流が流れ始め再び電流は増大する (p-1 または p-1 を)。一方、逆方向電圧を印加した場

図 III. 1.14 トンネルダイオード (エサキダイオード) の動作原理

合は、価電子が伝導帯にトンネルし、電流は単調増加する(f1 または f2)。エサキダイオードは高速動作が可能であるが、2 端子素子であるため入力と出力の分離が難しく、あまり実用されていない。

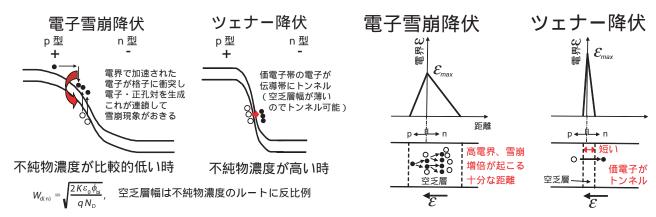

#### ・p-n 接合の降伏現象

p-n 接合に印加する逆バイアス電圧を大きくしていくと電流が急激に増大する。これを降伏現象と呼び、その機構には2種類ある(図 III.1.15)。電子雪崩降伏(アバランシェ降伏:Avalanche breakdown)と、ツェナー降伏(Zener breakdown)と呼ばれるトンネル現象である。不純物濃度が比較的低い場合には、十分な幅の空乏層が形成されるため、その中で電子雪崩増倍が起こる。1個の電子が格子に衝突し電子と正孔を生成し、その結果生じた電子と正孔が格子に衝突して、さらに多数の電子・正孔対を発生させ(衝突電離と呼ぶ)電子・正孔対の数がねずみ算的に増大する現象である。バンドギャップの6倍を越える電圧で起こる。一方、高い不純物濃度をもつp-n 接合では、空乏層幅が薄いため、電子雪崩より先にトンネル現象によって電流が増加する。バンドギャップの4倍以下の電圧で起こる。

図 III.1.15 p-n 接合の 2 種類の降伏現象

#### ・省エネルギーデバイス用半導体

二酸化炭素排出量削減は、地球環境保全のために極めて重要である。原子力エネルギーは二酸化炭素を排出することこそないが、2011.3.11 東北関東大震災で露呈されたように安全を保証することができない。有効な方法の一つは、無駄を省くことで、省電力デバイスが注目されている。

表 II.1 に示した半導体の中で、省電力デバイス用半導体として注目されているのが、SiC と GaN である。これらは耐圧が Si に比べて 10 倍程度大きく、熱伝導度も  $1.5 \sim 2.5$  倍と大きい。 $p^+-n$  片側階段接合ダイオードを例に取ると、(III・ $1\cdot 9$ ) を (III・ $1\cdot 4$ ) に代入すると分かるように電界強度は p-n 接合界面で最大値を取り、その値は不純物濃度の 1/2 乗にほぼ比例する ( $\phi_{bi}$  はバンドギャップで飽和する)。一方、抵抗は不純物濃度が高いほど低くなる(図 II.5.5)から、不純物濃度が高いほど直列抵抗による電力損失を小さくできる。耐圧が 10 倍大きい半導体材料を用いて p-n 接合ダイオードを形成すれば、不純物濃度を 100 倍大きくでき、直列抵抗を 1/100 に下げられ電力損失を 1/100 にすることができる。また、熱伝導度が大きいことは放熱効果が高く小型化に有利である。このように、SiC や 1/100 保存 1/100 に下げられているが、Si に比べて結晶品質、信頼性、製作プロセス、価格などの点で問題が残されており、その改善努力が続けられている。

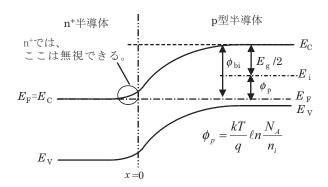

【例題 III. 1】 Si 片側階段  $n^+-p$  接合  $(N_D>>N_A, N_A=1 \times 10^{15} cm^{-3})$  において、印加電圧 0V および逆バイアス電圧 5V 印加時の空乏層幅を計算せよ。ただし、 $n^+$  半導体のフェルミレベルは伝導帯の底  $E_C$  に一致すると仮定せよ。温度は 300K とする。

#### ♦解答♦

(III・1・9) の

$$n$$

を  $p$  に、 $N_{\mathrm{D}}$  を  $N_{\mathrm{A}}$  に置き換えた式  $W_{d(p)} = \sqrt{\frac{2K\varepsilon_{0}\left(\phi_{bi} + V\right)}{qN_{\mathrm{A}}}}$  を用いて計算する。

図 III. 1.16 より内蔵電位は、 $\phi_{bi}=E_g/2+\phi_p$ .

$(III \cdot 1 \cdot 16)$

次に、図 III. 1. 16 の中に示された式 [(II·4·20) を eV 単位で表記] を用いて  $\phi_p$  を計算する。

$$\phi_p = \frac{kT}{q} \ell n \left( \frac{N_A}{n_i} \right) = 26 \times 10^{-3} \ell n \left( \frac{1.0 \times 10^{15}}{1.5 \times 10^{10}} \right) = 26 \times 10^{-3} \times 11.1 = 0.289 \text{ (eV)}$$

これを (III· 1· 16) に代入すると、 $\phi_{bi}$ =1.12/2+0.289=0.849 (eV). この値を  $W_{d(p)}$ の式に代入すると、

$$\begin{split} W_{\rm d(p)} &= \sqrt{\frac{2K\varepsilon_0(\phi_{\rm bi} + V)}{qN_{\rm A}}} = \sqrt{\frac{2\times11.7\times8.854\times10^{-14}\times(0.849 + V)}{1.6\times10^{-19}\times1.0\times10^{15}}} = \sqrt{1.29\times10^{-8}\times(0.849 + V)} \\ \text{For } V &= 0 \text{ V} \qquad W_{\rm d(p)} = \sqrt{1.09\times10^{-8}} = 1.05\times10^{-4} \text{ (cm)} = 1.05 \text{ ($\mu$ m)} \\ \text{For } V &= 5 \text{ V} \qquad W_{\rm d(p)} = \sqrt{7.55\times10^{-8}} = 2.75\times10^{-4} \text{ (cm)} = 2.75 \text{ ($\mu$ m)} \end{split}$$

図 III. 1.16 n<sup>†</sup>-p 片側階段接合のエネルギーバンドダイヤグラム

計算上の留意点

- 単位系を統一する

(cmとmを混在させない、℃とK、eVとJ単位には要注意)

- 2. 常用対数  $\log($  対数の底は 10) と自然対数 $\ell n$  (対数の底は e=2.71828) に注意

## III - 2 MOS 構造

MOS 構造とは、Metal-Oxide-Semiconductor 積層構造のことである。図 I.2.1 のゲート直下部分の構造に相当し、MOS トランジスタの心臓部である。

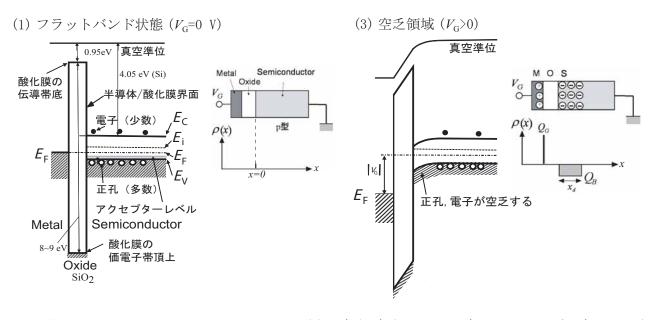

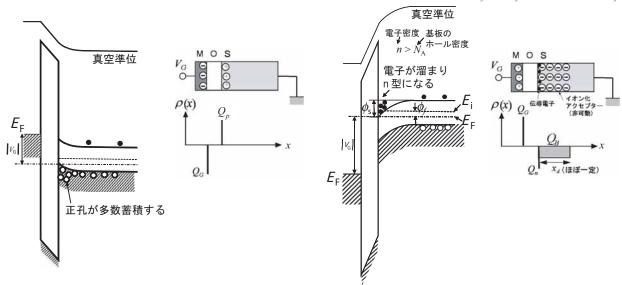

p型半導体を用いた MOS 構造のエネルギーバンドダイヤグラムと電荷分布を図 III. 2.1 に示す。金属電極に印加する電圧に応じて、フラットバンド状態、蓄積領域、空乏領域、反転領域(より正確には弱反転と強反転に分けられる)の 4 つの領域に分けられる。簡単のため、金属と半導体の仕事関数は等しいと仮定した。

## (1) フラットバンド状態 ( $V_G=0$ V)

金属電極に印加する電圧  $V_G$ =0 V の時は、金属、酸化膜、半導体全て等電位でバンドは平ら (フラット) である。この状態をフラットバンド状態と呼ぶ。金属と半導体の仕事関数が異なる場合は、その差分の電圧が、酸化膜と半導体に分配される。

## (2) 蓄積領域 (V<sub>G</sub><0)

## (2) 蓄積領域 ( $V_{G}$ <0)

(4) 反転領域 ( $V_G$ >0,弱反転 :2 $\phi_f$ > $\phi_s$ > $\phi_f$ ,強反転 : $\phi_s$ >2 $\phi_f$ )

図 III. 2.1 MOS 構造のエネルギーバンドダイヤグラムと電荷分布

$V_{G}$ <0 になるとバンドは図のように曲がり、半導体 / 酸化膜界面に多数キャリアである正孔が多数蓄積する。この電圧領域を蓄積領域と呼ぶ。

#### (3) 空乏領域 (V<sub>G</sub>>0)

$V_{\rm G}>0$  になるとバンドは図のように曲がり、半導体表面には、p-n 接合と同様キャリアの枯渇した空乏層が形成される。この領域を空乏領域と言う。

#### (4) 反転領域

• 4-1 弱反転領域 ( $V_G$ >0,  $\phi_t < \phi_s < 2\phi_t$ )

印加電圧が大きくなり、半導体表面のバンドの曲がり $\phi_s$ が $\phi_f$ を越えると、半導体表面のキャリア密度は、p型基板であるにもかかわらず、電子密度の方がホール密度よりわずかに大きくなるので弱反転領域と呼ぶ。表面の電子を反転電荷と呼ぶ。この領域では反転電荷(電子)密度 nは真性キャリア密度  $n_i$ より大きく、基板のホール密度  $N_A$ より小さい  $(n_i < n < N_A)$ 。ここで、 $\phi_f$ は 真性フェルミレベル  $E_i$  と、実際のフェルミレベル  $E_F$  とのエネルギー差  $\phi_f$  =  $E_i$  -  $E_F$  で、次式で与えられる。

$$\phi_f = \frac{kT}{q} \ln(\frac{N_A}{n_i}) \tag{III-2.1}$$

#### • 4-2 強反転領域 ( $V_{\rm G} > 0$ , $\phi_{\rm s} > 2\phi_{\rm f}$ )

印加電圧がさらに大きくなり、半導体表面のバンドの曲がり  $\phi_s$  が  $2\phi_f$  を越えると、半導体表面の電子密度が p 型基板のホール濃度より大きくなる  $(n>N_A)$ 。この領域を強反転領域と呼ぶ。強反転領域では、酸化膜電界はほとんど反転電荷で終端され、空乏層幅は飽和する(後述)。

以上が定性的説明であるが、定量的には以下のようになる。

基本方程式は,次のポアソン方程式である。座標xは図 III.2.1 のように取る。

$$\frac{d^2\varphi(x)}{dx^2} = -\frac{\rho(x)}{\varepsilon_s}, \qquad \rho(x) = q(p(x) - n(x) - N_A^{-1})$$

(III· 2· 2)

$$= p_0 \exp\left(-\frac{q}{kT}\varphi\right), \ n(x) = (n_i^2/p_0) \exp\left(\frac{q}{kT}\varphi\right), \ N_A = p_0 - (n_i^2/p_0) \ ,$$

(III-2-3)

$N_A^-$ はイオン化アクセプターの密度であり、中性領域での電荷中性条件より求まる。 $p_0$ は p 型中性領域のホール密度で  $N_A$ (p 型基板のアクセプター密度 ) **で**近似できる。(III・2・2) は、0 バイアスでは (II・4・18) で与えられるキャリア密度が、(II・4・3) よりわかるように電位  $\phi$  の下では  $E_F$ - $E_V$  が  $\phi$  だけシフトすることに由来する。(III・2・3) と  $p_0$ = $N_A$  を (III・2・2) に代入して次式を得る。

$$\frac{d^2\phi(x)}{dx^2} = -\frac{q}{\varepsilon_c} \left[ N_A (e^{-q\phi/kT} - 1) - (n_i^2/N_A)/(e^{q\phi/kT} - 1) \right]$$

(III· 2· 4)

境界条件は、

$$\phi(0) = \phi_s$$

,  $\phi(\infty) = 0$ ,  $\frac{d\phi}{dx}(\infty) = 0$  (III・2・5)

微分方程式 (III·2·4) は、解析的には解けない。しかし、次のように、半導体表面の電界と半導体中の電荷総量についての解析解は得られる。

$$\frac{d^2\phi}{dx^2} = A$$

の時,  $\left(\frac{d\phi}{dx}\right)^2 = 2\int\!\!Ad\phi$  を利用する。

証明:上式を

$$x$$

で微分すると、 $2\frac{d\phi}{dx}\frac{d^2\phi}{dx^2}=2A\frac{d\phi}{dx}\rightarrow \frac{d^2\phi}{dx^2}=A$ .

この公式を (III·2·4) に適用すると、電界 $\varepsilon$ が電位 $\phi$ の関数として次のように表せる。

$$\mathcal{E}^{2}(x) = \left(\frac{d\phi}{dx}\right)^{2} = \frac{2kTN_{A}}{\varepsilon_{s}} \left[ \left(e^{-q\phi/kT} + \frac{q\phi}{kT} - 1\right) + \frac{n_{i}^{2}}{N_{A}^{2}} \left(e^{q\phi/kT} - \frac{q\phi}{kT} - 1\right) \right]$$

(III· 2· 6)

図 III. 2.2 表面ポテンシャルと半導体中の全電荷量の関係

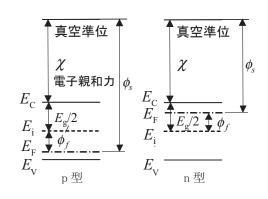

図 III. 2.3 半導体の仕事関数

x=0 で  $\phi=\phi_s$ ,  $\mathcal{E}=\mathcal{E}_s$  とし、半導体全体を囲う閉曲面に対してガウスの法則を適用すると、半導体内に誘起される単位面積あたりの総電荷量  $Q_s$  は、次式となる。

$$Q_{s} = -\varepsilon_{s} \mathcal{E}_{s}$$

$$= \pm \sqrt{2\varepsilon_{s}kTN_{A}} \left[ \left( e^{-q\varphi_{s}/kT} + \frac{q\varphi_{s}}{kT} - 1 \right) + \frac{n_{i}^{2}}{N_{A}^{2}} \left( e^{q\varphi_{s}/kT} - \frac{q\varphi_{s}}{kT} - 1 \right) \right]^{1/2}$$

(III· 2· 7)

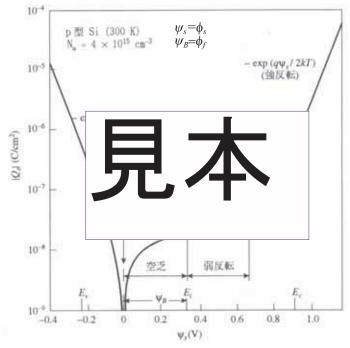

この関数を図示すると図 III. 2.2 となる。

- (1) フラットバンド状態 ( $V_G=0$  V) では、全電荷量  $Q_s$  はゼロである。

- (2) 蓄積領域  $(V_{G} < 0)$  では、 $Q_s$  は $\exp(q|\phi_s|/2kT)$ に比例し、 $\phi_s$  のわずかな変化に対して急激に変化する。

- (3) 空乏領域 ( $V_{\rm G}>0$ ) では、 $Q_{\rm s}$  は $\sqrt{\phi_{\rm s}}$  に比例して緩やかに変化する。この関係は p-n 接合のときの空乏層中の電荷と電圧の関係 (III·1·9) と同じである。

- (4) 強反転領域  $(V_G>0,\phi_s>2\phi_f)$  では、 $Q_s$  は $\exp(q\phi_s/2kT)$ に比例し、 $\phi_s$  のわずかな変化に対して急激に変化する。強反転領域では、ゲート電圧を増加させた時、反転電荷密度が大きく増加するので、表面電位は極わずか増加するだけでよく、空乏層幅はこれ以上ほとんど変化しなくなる。 $\phi_s=2\phi_f$  の時強反転状態が始まる。この時のゲート電圧  $V_T$  を反転電圧と呼び、次式で与えられる。

$$V_T = -\frac{Q_S(x_d(inv))}{C_{ox}} + \phi_s(inv) = \frac{\sqrt{2\varepsilon_s q N_A(2\phi_f)}}{C_{ox}} + 2\phi_f$$

(III· 2·8)

ここに、 $Q_s$  は半導体中の全電荷(空乏層電荷と反転電荷の和)で、強反転開始の時は反転電荷《空乏層電荷なので III・ $2\cdot 8$  式のように空乏層電荷で近似できる。 $C_{ox}$  は単位面積当たりの酸化膜容量で、

$$C_{ox} = \frac{\mathcal{E}_{ox}}{d_{ox}}$$

,  $\mathcal{E}_{ox}$  は酸化膜の誘電率、 $d_{ox}$  は酸化膜厚である。 (III- 2-9)

ゲート金属と半導体間に仕事関数差があり、酸化膜中に電荷がある時は、反転電圧は次式となる。

$$V_T = \frac{\sqrt{2\varepsilon_s q N_A(2\phi_f)}}{C_{ox}} + 2\phi_f + \phi_{ms} - \frac{Q_{ox}}{C_{ox}}$$

(III· 2· 10)

ここで、 $Q_{ox}$ は酸化膜中の有効電荷、 $\phi_{ms}$ はゲート金属と半導体の仕事関数差で次の式で与えられる。

$$Q_{ox} = \frac{1}{d} \int_0^d x \rho_{ox} dx$$

(III · 2 · 11)

$$\phi_{ms} = \phi_m - \phi_s = \phi_m - (\chi + E_g/2 + \phi_f)$$

(半導体基板が p 型の場合) (III・2・12)  $\phi_{ms} = \phi_m - \phi_s = \phi_m - (\chi + E_g/2 - \phi_f)$  (半導体基板が n 型の場合)  $\phi_{ms}$  導出のための図を図 III. 2. 3 に示す。

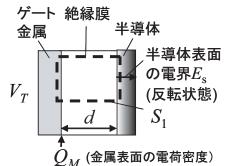

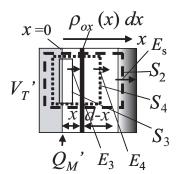

【**例題 III. 2**】 酸化膜中の電荷が反転電圧に影響を及ぼす時の有効電荷の式 (III· 2· 11) を導け。

## **◆解答**◆

(a) 絶縁膜中に電荷のない時

図 III. 2.4(a) において、閉曲面 S<sub>1</sub>(断面積 1) にガウスの法則を 適用して、半導体表面の電界 E。は、

$$E_s = \frac{Q_M}{\varepsilon_s}$$

( $\varepsilon_s$  は半導体の誘電率) (III· 2·13)

同様に閉曲面 $S_2$ ,  $S_3$ ,  $S_4$ , (全て断面積1) にガウスの法則を適用して、

$$E_{s} = \frac{Q_{M}' + \rho_{ox}(x)dx}{\varepsilon}$$

(III· 2· 14)

x=0とx=xの間の電界 $E_3$ は、

$$x=x$$

の間の電界  $E_3$  は、

$$E_3 = \frac{Q_M'}{\varepsilon_{ox}} \quad (\varepsilon_{ox} \text{ は絶縁膜の誘電率}) \quad (III \cdot 2 \cdot 15)$$

$$x=x$$

と  $x=d$  の間の電界  $E_4$  は、

$$E_4 = \frac{Q_M' + \rho_{ox}(x) dx}{\varepsilon_{ox}}$$

(III・2・16)

一方、しきい値電圧  $V_{\rm T}, V_{\rm T}$  は、

$$V_{T} = \frac{Q_{M} \cdot d}{\varepsilon_{ar}} + 2\phi_{s} \tag{III} \cdot 2 \cdot 17)$$

$$V_T' = E_3 \cdot x + E_4 \cdot (d - x) + 2 \phi_s$$

(III · 2 · 18)

によるしきい値電圧の変化

図 III. 2.4 ゲート酸化膜中の電荷によ

(b) 絶縁膜中の電荷 $\rho_{ox}(x)$  dx (III·2·17), (III·2·18) に (III·2·15), (III·2·16) を代入して、 (III·2·13)=(III·2·14) を用いると、

図 III. 2.4 ゲート酸化膜中の電荷によるしきい値電圧の変化

$$V_T'-V_T = -\frac{x\cdot \rho_{ox}(x)dx}{\varepsilon_{ox}} + \frac{(Q_M'+\rho_{ox}(x)dx-Q_M)d}{\varepsilon_{ox}}$$

$$= -\frac{x\cdot \rho_{ox}(x)dx}{\varepsilon_{ox}}$$

$$(III\cdot 2\cdot 19)$$

従って酸化膜中の全電荷分布による反転電圧の変化  $\Delta V_T$  は、次式となる。

$$\Delta V_T = -\frac{1}{C_{ox}} \left[ \frac{1}{d} \int_0^d x \cdot \rho_{ox}(x) dx \right]$$

(III· 2· 20)

酸化膜中の電荷には、可動イオン (Na<sup>+</sup>, K<sup>+</sup> など)、固定電荷、絶縁膜 / 半導体界面トラップ電荷がある。

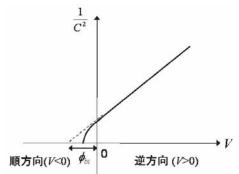

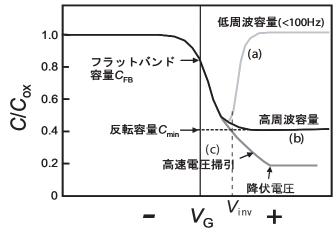

#### ・MOS 構造の容量一電圧特性

MOS 構造の容量一電圧特性 (図 III. 2.5) を測定すると、酸化膜厚、半導体の不純物濃度、半導体 /酸化膜界面(表面)準位密度などが評価できる。

MOS 構造の微分容量 C は次式で与えられる。

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{dQ_s / d\phi_s}$$

(III· 2· 21)

$$\pm \mathcal{T}, \qquad \frac{dQ_s}{d\phi_s} = C_s$$

(III· 2· 22)

は半導体容量である。(III·2·21)は、次のように導かれる。

図 III. 2.5 MOS 構造の容量一電圧特性

ゲート電圧  $V_G$  は、酸化膜にかかる電圧  $V_{ox}$  と半導体にかかる電圧  $\phi_s$  の和なので、

$$V_{\rm G} = V_{\rm ox} + \phi_{\rm s} \tag{III} \cdot 2 \cdot 23)$$

微分して、

$$dV_{\rm G} = dV_{\rm ox} + d\phi_{\rm s}. \tag{III} \cdot 2 \cdot 24)$$

一方、図 III. 2.1(4) に示す中性条件を与える電荷分布より明らかなように、

$$Q_{\rm G} = -(Q_{\rm inv} + Q_{\rm dep}) = -Q_{\rm S}. \tag{III} \cdot 2 \cdot 25$$

ここで、 $Q_{G}$ はゲート電極電荷、 $Q_{inv}$ は反転電荷、 $Q_{dep}$ は空乏層電荷、 $Q_{S}$ は半導体内全電荷である。 また、測定微分容量Cは、次式で与えられる。

$$C = |dQ_{G}/dV_{G}| \tag{III-2.26}$$

(III·2·26) に、(III·2·24) と (III·2·25) を代入すると、

$$1/C = 1/(dQ_G/dV_{ox}) + 1/(dQ_s/d\phi_s)$$

(III· 2· 27)

となり、(III·2·21) が得られる。

半導体電荷 $Q_s$ は(III·2·7)によって $\phi_s$ の関数として与えられているので容量の解析解が得られる。 (1) フラットバンド容量  $C_{FB}$

(III·2·7) で、 $\phi_s \rightarrow 0$  とし、 $\exp(\phi_s/kT) \sim 1 + \phi_s/kT$  の近似を用いると、

$$\frac{1}{C_{FB}} = \frac{1}{C_{ox}} + \sqrt{\frac{kT}{\varepsilon_s q^2 N_A}} = \frac{1}{C_{ox}} + \frac{L_D}{\varepsilon_s}, \quad L_D \equiv \sqrt{\frac{\varepsilon_s kT}{q^2 N_A}}$$

(III· 2· 28)

ここに、L。はデバイ長と呼ばれ、電荷による電界の影響が及ぶ距離である。

- (2) 蓄積領域 ( $V_{G}$ <0) では、 $Q_{s}$  は $\exp(q|\phi_{s}|/2kT)$ に比例し、 $\phi_{s}$  のわずかな変化に対して急激に変化する ので、 $C_s$  は極めて大きくなる。その結果 C は急速に  $C_{\infty}$  に近づく。

- (3) 空乏領域  $(V_{\rm G}>0)$  では、 $Q_{\rm s}$  は $\sqrt{\phi_{\rm s}}$  に比例する。(III-2-7) の第1項の()内の $\phi_{\rm s}/kT$ のみを考えれ ばよく、 $Q_s = -\sqrt{2\varepsilon_s q N_A \phi_s}$ となる故、

$$C_s \equiv C_D = \sqrt{\frac{\varepsilon_s q N_A}{2\phi_s}} = \frac{\varepsilon_s}{W_d}, \qquad W_d = \sqrt{\frac{2\varepsilon_s \phi_s}{q N_A}}. \tag{III-2-29}$$

ここで、

$$W_{\rm d}$$

は p-n 接合の時の空乏層幅を与える式と同じであり、物理的描像も同様である。

従って、

$$\frac{1}{C} = \frac{1}{C_{ox}} + \sqrt{\frac{2\phi_s}{\varepsilon_s q N_A}} \quad . \tag{III-2.30}$$

すなわち、空乏領域では、正のゲート電圧を増加させていくと、容量は減少していく。

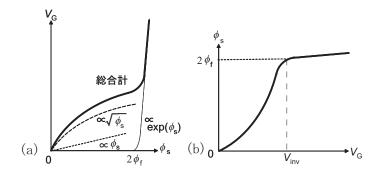

図 III. 2.6 (a) 半導体表面バンド曲がり  $\phi_s$  に対するゲート電圧  $V_G$  の変化。 (b) ゲート電圧  $V_G$  に対する半導体表面バンド曲がり  $\phi_s$  の変化。

(4) 強反転領域  $(V_G>0, \phi_s>2\phi_f)$  では、 $Q_s$  は $\exp(q\phi_s/2kT)$ に比例し、 $\phi_s$  のわずかな変化に対して急激に変化するので、 $C_s$  は極めて大きくなる。その結果 C は急速に  $C_{ox}$  に近づく。以上をまとめると、容量は図 III. 2. S(a) のような曲線を描く。

ここで、空乏層幅の電圧依存性について考察する。 $V_G = V_{\rm ox} + \phi_s$  の関係を図 III. 2.6 に示す。図 (a) に示すように、空乏領域では、 $V_G$  は $\sqrt{\phi_s}$  に比例する項と $\phi_s$  の和で与えられ、ゆっくりと増加する。 $\phi_s = 2\phi_f$  以上では、 $V_G$  は  $\exp(\phi_s)$  に比例して急激に増加する。縦軸と横軸を入れ替えて考えると(図 (b))、 $V_G$  を増加させていくと、空乏領域では、 $\phi_s$  は急激に増加、すなわち $\sqrt{\phi_s}$  に比例する空乏層幅が急激に拡がり、強反転状態( $\phi_s = 2\phi_f$ )に達すると、 $\phi_s$  は飽和する。すなわち空乏層は、最大空乏層幅  $W_{\rm dmax}$  に達し、それ以上はほとんど増加しなくなる。強反転条件に達する時( $\phi_s = 2\phi_f$ )のゲート電圧を反転電圧 ( $V_{\rm inv}$ ) と呼ぶ。 $W_{\rm dmax}$  は次式で与えられる。

$$W_{d\max} = \sqrt{\frac{2\varepsilon_s(2\phi_f)}{qN_A}} = \frac{2}{q}\sqrt{\frac{\varepsilon_s kT}{N_A} \ln\left(\frac{N_A}{n_i}\right)}$$

(III- 2- 31)

次に容量の周波数依存性について考える。反転電荷である電子は、p型半導体中の少数キャリアであり、熱励起によって発生するのみで、その発生時定数が長い (0.1-10s) ため、容量 C は測定周波数および電圧掃引のスピードによって次のように変化する (図 III. 2.5)。

(a) 低周波(<100Hz 程度)、遅い電圧掃引

この条件では、少数キャリア発生が印加する交流微小電圧および掃引するバイアス電圧変化に追随できるので、図 III. 2.5(a) のように電圧増加と共に  $C_{ox}$  に近づく。

(b) 高周波、遅い電圧掃引

高周波では、交流微小電圧の変化に少数キャリア発生が追随できなくなり、空乏層容量のみが測定される。電圧掃引は十分遅いので、反転層が形成され空乏層幅は $\phi_s=2\phi_f$ 以上ではほとんど増加しない。従って、容量は $\phi_s=2\phi_f$ で最小値 $C_{min}$ に達し、これ以下には減少しない(図 III. 2. 5(b))。  $C_{min}$  は、 $W_{dmax}$  で決まる空乏層容量と酸化膜容量の直列接続で与えられ、次式となる。

$$\frac{1}{C_{\min}} = \frac{1}{C_{ox}} + \frac{W_{d\max}}{\varepsilon_s} = \frac{1}{C_{ox}} + \sqrt{\frac{4kT \cdot \ell n(N_A/n_i)}{\varepsilon_s q^2 N_A}}$$

(III· 2· 32)

(c) 速い電圧掃引(高周波、低周波)

高周波では、印加微小交流電圧の変化に少数キャリア発生が追随できないため、空乏層容量のみが測定される。なおかつ、電圧掃引が速く、少数キャリアである電子の熱励起発生が追いつかないため、反転層が形成されない。従って、ゲート電圧増加と共に空乏層幅は $W_{dmax}$ 以上に増加し、容量は図 III. 2.5(c) のように変化する。p-n 接合の時と同様、降伏現象が起こる電圧に達すると容量は変化しなくなる。

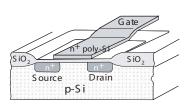

## III・3 MOS トランジスタ

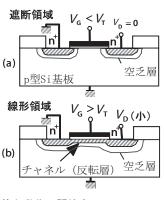

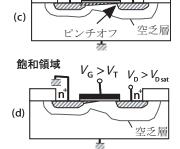

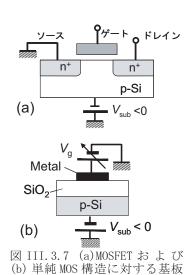

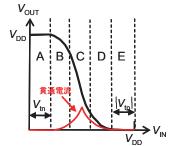

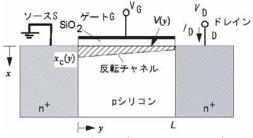

MOSFET (MOS Field Effect Transistor) の構造および電気的特性の模式図を図 III. 3.1 と III. 3.2 に示す。ゲート直下に MOS 構造があり、その両側に p-n 接合が隣接して配置された構造である。 N(f+r) MOS トランジスタの場合、ゲートの両側の n+ (濃度の濃い n 型を + で表わす) を、ソースおよびドレインと呼ぶ。ソースードレイン間に流れる電流(ドレイン電流)と電圧の関係を、ゲートーソース電圧をパラメータにプロットしたものが図 III. 3.2 である。図 III. 3.3 に各領域における反転層と空乏層の状態を示す。また、図 III. 3.4 に立体的なエネルギーバンドダイヤグラムを示す。

#### (1) 遮断領域

ゲート電圧が MOS 構造の反転電圧より小さい場合は、ソースードレイン間に電流は流れない。この領域を遮断領域と呼ぶ。

#### (2)線形領域

ゲートに、反転電圧以上の正電圧を印加すると、ゲート直下の半導体表面にn型の反転層(トランジスタの場合、チャネルと呼ぶ)が形成され、ソース、ドレインと反転層が繋がりソースードレイン間に電流が流れる(図 III.3.3 (b), III.3.4 (c))。ドレイン電流が流れはじめるゲート電圧 $V_G$ を、トランジスタの「しきい値電圧」と呼び $V_T$ で表す。n チャネルトランジスタのしきい値電圧は、MOS 構造の反転電圧にほぼ等しく次式で与えれられる(再掲)。

$$V_T = \frac{\sqrt{2\varepsilon_s q N_A(2\phi_f)}}{C_{...}} + 2\phi_f + \phi_{ms} - \frac{Q_{ox}}{C_{ox}}$$

(III· 2· 10)

トランジスタのしきい値電圧は、反転層容量その他の効果により、 上式の値よりいくぶん高くなる。ドレイン電圧が小さい領域では、 ドレイン電流はドレイン電圧にほぼ比例するので、この領域を線 形領域と言う。

図 III. 3.1 NMOS トランジスタ の構造

ドレイン電圧 V<sub>D</sub>

図 III.3.2 MOS トランジス タの特性

#### 飽和動作の開始点

図 III. 3.3 MOS トランジスタ の各動作領域

図 III.3.4 MOS トランジスタの立体的 エネルギーバンドダイヤグラム

図 III. 3.5 ピンチオフ状態の電子流れ の様子

図 III. 3.6 ピンチオフ状態の電子流 のイメージ図

ちなみに、n型基板を用いたpチャンネルトランジスタのしきい値電圧は、次式となる。

$$V_T = -\frac{\sqrt{2\varepsilon_s q N_D(2\phi_f)}}{C_{ox}} - 2\phi_f + \phi_{ms} - \frac{Q_{ox}}{C_{ox}}$$

(符号に注意) (III・3・1)

#### (3) 飽和領域

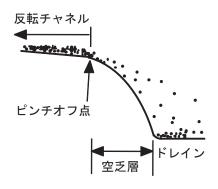

チャネル長が長い場合、しきい値電圧以上のゲート電圧を印加した状態でドレイン電圧を大きくしていくと、ドレイン電流はやがて飽和する。この領域を飽和領域と言う。この領域では、ドレイン近傍の空乏層が基板側に拡がり、反転層が形成されない領域ができる。反転層がなくなる点をピンチオフ点と呼ぶ。飽和領域の始まりでは、ピンチオフ点はドレイン端近傍にあり、ドレイン電圧を増大させるとピンチオフ点はソース側に移動していく。この様子を以下に詳しく説明する。

基板に対してドレインに  $V_D > 0$  の逆方向電圧を印加すると、ドレイン空乏層端の p 型基板の電子密度は、  $n_{n0} \exp(-qV_D/kT) \tag{III-3-2}$